コンピュータアーキテクチャのエッセンス

カマー博士が解く「プログラマから見たコンピュータの真の姿」

本書は、計算機のプロとなる人を対象にコンピュータの基本原理を体系的に学習できるよう構成しています。またIT技術者をはじめ電子、電気、技術士などコンピュータを取り扱うすべての人が基礎を学ぶ教科書として最適です。特にいま注目を集めている組み込みに必要な人材である「マイコン少年」を育成する教科書として重要視されています。(2007 年に第一世代のマイコン少年が第一線の現場から姿を消そうとしています。)そしてETSS の必読書としても重要な位置にあると同時にITSS でも不可欠な存在になっています。『プログラムはなぜ動くのか』のようなトピックスを集めただけの構成でなく、体系的に本質を習得できるのが特徴です。

第1章 序論と概要

1.1 アーキテクチャの重要性

1.2 基本を学ぶ

1.3 この教科書の構成

1.4 何を省略するか

1.5 アーキテクチャと設定という用語

1.6 まとめ

第1部 ディジタル論理回路とデータ表現の基礎―コンピュータを構成する基盤

第2章 ディジタル論理回路の基礎

2.1 はじめに

2.2 電子工学的用語:電圧と電流

2.3 トランジスタ

2.4 論理ゲート

2.5 ゲートに対応するシンボル

2.6 ゲートをトランジスタから作る

2.7 ゲート間の結線

2.8 1つの集積回線内の複数ゲート

2.9 組み合わせ回路以上の機能の必要性

2.10 状態を扱う回路

2.11 状態遷移図

2.12 バイナリカウンタ

2.13 クロックとシーケンス

2.14 重要な概念「フィードバック」

2.15 シーケンスの開始

2.16 ソフトウェアによる繰り返しとハードウェアの複製

2.17 ゲートとチップの最小化

2.18 予備のゲートを使う

2.19 電源の分配と熱の消散

2.20 タイミング

2.21 物理的サイズとプロセス技術

2.22 回路基板と層

2.23 抽象化のレベル

2.24 まとめ

第3章 データやプログラムの表現

3.1 はじめに

3.2 ディジタル論理回路と抽象化

3.3 ビットとバイト

3.4 バイトサイズと取り得る値

3.5 2進算術

3.6 16進記法

3.7 16進と2進の定数の記法

3.8 文字セット

3.9 Unicode

3.10 符号なし整数とオーバーフローとアンダーフロー

3.11 ビットやバイトの番号付け

3.12 符号付き整数

3.13 2つの補数の例

3.14 符号拡張

3.15 浮動小数点

3.16 特別な値

3.17 IEEE浮動小数点値の範囲

3.18 データの集約

3.19 プログラムの表現

3.20 まとめ

演習問題

第2部 プロセッサ―計算を駆動するエンジン

第4章 さまざまなプロセッサと計算エンジン

4.1 はじめに

4.2 フォン・ノイマンアーキテクチャ

4.3 プロセッサの定義

4.4 プロセッサの分類

4.5 階層構造と計算エンジン

4.6 通常のプロセッサの構造

4.7 算術論理ユニット(ALU)の定義

4.8 プロセッサの種類と役割

4.9 プロセッサ技術

4.10 プログラム内蔵方式

4.11 フェッチー実行サイクル

4.12 クロック周波数と命令ルート

4.13 制御:始めること、そして止めること

4.14 フェッチー実行サイクルの始動

4.15 まとめ

演習問題

第5章 さまざまなプロセッサと命令セット

5.1 はじめに

5.2 計算能力、便利さ、コスト

5.3 命令セットとその表現

5.4 オペコード、オペランド、結果

5.5 典型的な命令形式

5.6 可変長命令と固定長命令

5.7 汎用レジスタ

5.8 浮動小数点レジスタとレジスタ識別(ID)

5.9 レジスタを使ったプログラミング

5.10 レジスタバンク

5.11 複雑な命令セットと縮小した命令セット

5.12 RISC設計と実行パイプライン

5.13 パイプラインと命令ストール

5.14 パイプラインストールの他の要因

5.15 プログラマのための帰結

5.16 プログラミングとストール、そして何もしないという命令

5.17 フォワーディング

5.18 演算の型

5.19 プログラムカウンタ、フェッチー実行、分岐

5.20 サブルーチンコール、引数、レジスタウィンドウ

5.21 命令セット例

5.22 最小命令セット

5.23 直交性の原則

5.24 状態コードと条件分岐

5.25 まとめ

演習問題

第6章 オペランドアドレッシングと命令表現

6.1 はじめに

6.2 0、1、2、3-アドレス設計

6.3 オペランドのない命令

6.4 1オペランド命令

6.5 2オペランド命令

6.6 3オペランド命令

6.7 ソースオペランドと即値

6.8 フォン・ノイマンボトルネック

6.9 明示的または暗黙的なオペランドの符号化

6.10 複数の値を結合するオペランド

6.11 オペランド選択におけるトレードオフ

6.12 メモリにおける値と間接参照

6.13 オペランドアドレッシングモード

6.14 まとめ

演習問題

第7章 CPU:マイクロコード、保護、およびプロセッサモード

7.1 はじめに

7.2 中央処理装置

7.3 CPUを複雑にするもの

7.4 実行モード

7.5 逆方向の互換性

7.6 モード変更

7.7 特権と保護

7.8 複数レベルの保護

7.9 マイクロコード命令

7.10 さまざまなマイクロコード

7.11 マイクロコードの利点

7.12 プログラマから見たマイクロコード

7.13 垂直型マイクロコード

7.14 水平型マイクロコード

7.15 簡単な水平型マイクロコード

7.16 典型的水平型マイクロコード

7.17 複数のサイクルを必要とする操作

7.18 水平型マイクロコードと並列実行

7.19 先読みと高性能実行

7.20 並列性と実行順序

7.21 アウトオブオーダー実行

7.22 条件分岐と分岐予測

7.23 プログラマのための結果

7.24 まとめ

演習問題

第8章 アセンブリ言語とプログラミングパラダイム

8.1 はじめに

8.2 高レベル言語の特質

8.3 低レベル言語の性質

8.4 アセンブリ言語

8.5 アセンブリ言語の構文とオペコード

8.6 オペランドの順番

8.7 レジスタ名

8.8 オペランドの型

8.9 アセンブリ言語のパラダイムと用法

8.10 条件実行のアセンブリコード

8.11 条件分岐のアセンブリコード

8.12 繰り返し回数が明示されているアセンブリコード

8.13 繰り返し回数未定義のアセンブリコード

8.14 手続き呼び出しのアセンブリ言語

8.15 引数付き手続きを呼び出すアセンブリ言語のコード

8.16 プログラマへもたらされるもの

8.17 関数呼び出しのアセンブリ言語のコード

8.18 アセンブリ言語と高レベル言語の相互呼び出し

8.19 変数と記憶域のアセンブリ言語のコード

8.20 2パスアセンブラ

8.21 アセンブリ言語のマクロ

8.22 まとめ

第3部 メモリ―プログラムとデータ 記憶装置技術

第9章 メモリと記憶装置

9.1 はじめに

9.2 定義

9.3 メモリのキーとなる見方

9.4 メモリ技術の特徴

9.5 メモリ階層の重要な概念

9.6 命令メモリとデータメモリ

9.7 フェッチーストアパラダイム

9.8 まとめ

第10章 物理メモリと物理アドレス

10.1 はじめに

10.2 コンピュータメモリの特徴

10.3 スタティックRAMとダイナミックRAM

10.4 メモリ技術の基準

10.5 容量

10.6 読み込みおよび書き込み性能の分離

10.7 遅延とメモリコントローラ

10.8 同期メモリ技術

10.9 マルチデータレートメモリ技術

10.10 メモリ技術の例

10.11 メモリ構成

10.12 メモリアクセスとメモリバス

10.13 メモリ転送サイズ

10.14 物理アドレスとワード

10.15 物理メモリ操作

10.16 ワードサイズと他のデータ型

10.17 極端な場合:バイトアドレッシング

10.18 ワード転送によるバイトアドレッシング

10.19 2のべき乗を使う意味

10.20 バイト整列とプログラミング

10.21 メモリ容量とアドレス空間

10.22 ワードアドレッシングによるプログラミング

10.23 メモリ容量の計算

10.24 ポインタとデータ構造

10.25 メモリダンプ

10.26 間接参照と間接オペランド

10.27 メモリバンクとインターリーブ

10.28 連想メモリ

10.29 3値CAM

10.30 まとめ

演習問題

第11章 仮想メモリの技術と仮想アドレス

11.1 はじめに

11.2 定義

11.3 仮想的な例:バイト単位の番地付け

11.4 仮想メモリ

11.5 物理メモリシステムを多重化するインタフェース

11.6 アドレス変換またはアドレスマッピング

11.7 算術演算を避ける

11.8 連続でないアドレス空間

11.9 他のメモリ構成

11.10 仮想メモリの動機

11.11 複数の仮想空間と多重プログラミング

11.12 仮想化の複数のレベル

11.13 仮想アドレス空間の動的な生成

11.14 ベース―範囲レジスタ

11.15 仮想空間の変更

11.16 仮想メモリとベース―範囲と保護

11.17 セグメンテーション

11.18 デマンドページング

11.19 デマンドページングのハードウェアとソフトウェア

11.20 ページ置き換え

11.21 ページングの用語とデータ構造

11.22 ページングシステムにおけるアドレス変換

11.23 2のべき乗を使う

11.24 存在ビットと使用ビット、それに被変更ビット

11.25 ページ表記憶

11.26 ページングの効果と変換側付きバッファ

11.27 プログラマに対する結果

11.28 まとめ

演習問題

第12章 キャッシュとキャッシュ技術

12.1 はじめに

12.2 定義

12.3 キャッシュの特徴

12.4 キャッシュ技術の重要性

12.5 キャッシュ技術の例

12.6 キャッシュにおける用語

12.7 最善、最悪の場合のキャッシュ性能

12.8 典型的な連続アクセスにおけるキャッシュ性能

12.9 キャッシュ置き換えポリシー

12.10 LRU置き換え

12.11 多重レベルキャッシュ階層

12.12 先読みキャッシュ

12.13 メモリシステムにおけるキャッシュ

12.14 キャッシュとしてのTLB

12.15 キャッシュ技術としてのデマンドページング

12.16 物理メモリキャッシュ

12.17 ライトスルーとライトバック

12.18 キャッシュの一貫性(コヒーレンス)

12.19 L1、L2、L3キャッシュ

12.20 L1、L2、L3キャッシュの容量

12.21 命令とデータキャッシュ

12.22 仮想メモリキャッシュ技術とキャッシュフラッシュ

12.23 メモリキャッシュの実現

12.24 ダイレクトマッピングメモリキャッシュ

12.25 効率化のための2のべき乗

12.26 セットアソシアティブメモリキャッシュ

12.27 プログラマにとっての重要性

12.28 まとめ

演習問題

第4部 入出力―外部との接続とデータ移動

第13章 入出力の概念と用語

13.1 はじめに

13.2 入力と出力の装置

13.3 外部装置の制御

13.4 データ転送

13.5 直列型(シリアル)と並列型(パラレル)データ転送

13.6 自己同期型データ

13.7 全二重と半二重通信

13.8 インタフェースの遅延と流通

13.9 多重化という基本アイディア

13.10 1つの外部インタフェースに複数の装置

13.11 入出力のプロセッサからの見え方

13.12 まとめ

第14章 バスとバスアーキテクチャ

14.1 はじめに

14.2 バスの定義

14.3 プロセッサ、入出力、そしてバス

14.4 専有的バスと標準バス

14.5 共有バスとアクセスプロトコル

14.6 複数のバス

14.7 受動的で並列的な機構

14.8 物理的接続

14.9 バスインタフェース

14.10 アドレスライン、コントロールライン、データライン

14.11 フェッチーストアパラダイム

14.12 バスを介したフェッチーストア

14.13 バスの幅

14.14 多重化

14.15 バス幅とデータのサイズ

14.16 バスアドレス空間

14.17 潜在的なエラー

14.18 アドレス配置とソケット

14.19 複数のバスか1つのバスか

14.20 フェッチーストアを装置に用いる

14.21 フェッチーストアを使った装置制御の例

14.22 インタフェースの操作

14.23 非対称な割り当て

14.24 メモリと装置の統一的なアドレッシング

14.25 アドレス空間の穴

14.26 アドレスマップ

14.27 バスに対するプログラムインタフェース

14.28 2つのバスの橋渡し

14.29 主バスと補助バス

14.30 プログラマにはどう見えるか

14.31 スイッチング機構

14.32 まとめ

演習問題

第15章 プログラム駆動入出力と割り込み駆動入出力

15.1 はじめに

15.2 入出力パラダイム

15.3 プログラム駆動入出力

15.4 動機

15.5 ポーリング

15.6 ポーリングのコード

15.7 制御・状態レジスタ

15.8 プロセッサの使用とポーリング

15.9 第1世代、第2世代、そして第3世代のコンピュータ

15.10 割り込み駆動入出力

15.11 ハードウェアの割り込み機構

15.12 割り込みとフェッチー実行サイクル

15.13 割り込みの処理

15.14 割り込みベクタ

15.15 初期化と割り込みの許可/不許可

15.16 割り込みコードが割り込まれることの防止

15.17 割り込みの複数レベル

15.18 割り込みベクタの割り当てと優先度

15.19 動的バス接続と活線装着可能な装置

15.20 割り込みが優れている点

15.21 賢い装置と入出力性能の改善

15.22 ダイレクトメモリアクセス(DMA)

15.23 バッファの数珠繋ぎ

15.24 撒き読み込み操作と集め書き出し操作

15.25 操作の数珠繋ぎ

15.26 まとめ

演習問題

第16章 装置、入出力、そしてバッファリングに対するプログラマの視点

16.1 はじめに

16.2 デバイスドライバの定義

16.3 装置独立、カプセル化と隠ぺい

16.4 デバイスドライバの制御例

16.5 2つのタイプの装置

16.6 デバイスドライバの制御例

16.7 待ち行列を使った出力操作

16.8 割り込みの強制

16.9 待ち行列化された入力操作

16.10 双方向の転送をサポートする装置

16.11 「非同期なプログラミングの枠組み」対「同期的なプログラミングの枠組み」

16.12 非同期性、賢い装置と相互排除

16.13 アプリケーションプログラムから見た入出力

16.14 実行時入出力ライブラリ

16.15 ライブラリ/OS二分論

16.16 OSが提供する入出力操作

16.17 入出力操作のコスト

16.18 システムコールオーバーヘッドを減らす

16.19 バッファリングの重要な概念

16.20 バッファリングの実装

16.21 バッファのフラッシュ

16.22 入力のバッファリング

16.23 バッファリングの有効性

16.24 OS内でのバッファリング

16.25 キャッシュとの関連

16.26 例:UNIX標準入出力ライブラリ

16.27 まとめ

演習問題

第5部 高度な話題―並列性とパイプラインの基礎概念

第17章 並列化

17.1 はじめに

17.2 並列パイプラインアーキテクチャ

17.3 並列処理の特徴

17.4 「マイクロスコピック」対「マクロスコピック」

17.5 マイクロスコピック並列処理の例

17.6 マクロスコピック並列処理の例

17.7 「対称」対「非対称」

17.8 「細粒度並列処理」対「粗粒度並列処理」

17.9 「明示的並列処理」対「暗黙的並列処理」

17.10 並列アーキテクチャ

17.11 並列アーキテクチャの分類(フリンの分類)

17.12 単一命令単一データ流(SISD)

17.13 単一命令複数データ流(SIMD)

17.14 複数命令複数データ流(MIMD)

17.15 通信、協調、競合

17.16 マルチプロセッサの性能

17.17 プログラマへの影響

17.18 並列アーキテクチャの冗長性

17.19 分散、クラスコンピュータ

17.20 まとめ

演習問題

第18章 パイプライン

18.1 はじめに

18.2 パイプラインの概念

18.3 ソフトウェアパイプライン

18.4 ソフトウェアパイプラインの効率とオーバーヘッド

18.5 ハードウェアパイプライン

18.6 ハードウェアパイプラインによる処理効率の向上

18.7 パイプラインが利用可能な場合

18.8 処理分割の概念

18.9 パイプラインアーキテクチャ

18.10 パイプラインセットアップ、ストール、フラッシュタイム

18.11 スーパーパイプラインアーキテクチャの定義

18.12 まとめ

演習問題

第19章 性能評価

19.1 はじめに

19.2 計算能力と性能の評価

19.3 計算能力の測定

19.4 特定アプリケーションにおける命令数の測定

19.5 インストラクションミックス

19.6 標準ベンチマーク

19.7 入出力とメモリボトルネック

19.8 ハードウェアとソフトウェアの境界

19.9 最適化のために選択される項目

19.10 アムダールの法則と並列システム

19.11 まとめ

演習問題

第20章 アーキテクチャの例と階層構造

20.1 はじめに

20.2 アーキテクチャレベル

20.3 システムレベルアーキテクチャ:パーソナルコンピュータ

20.4 バス接続とブリッジ

20.5 制御チップと物理アーキテクチャ

20.6 仮想バス

20.7 通信速度

20.8 ブリッジの機能と仮想バス

20.9 ボードレベルアーキテクチャ

20.10 チップレベルアーキテクチャ

20.11 チップ内部の機能ユニットの構造

20.12 まとめ

20.13 コンピュータアーキテクチャの範囲を越えた構造

付録 コンピュータアーキテクチャコースのための実験

A1.1 はじめに

A1.2 実験のためのディジタルハードウェア

A1.3 ブレッドボード

A1.4 ブレッドボードの利用

A1.5 テスト

A1.6 電源とアースの接続

A1.7 実験結果

お問い合わせ

内容についてのお問い合わせは、正誤表、追加情報をご確認後に、お送りいただくようお願いいたします。

正誤表、追加情報に掲載されていない書籍内容へのお問い合わせや

その他書籍に関するお問い合わせは、書籍のお問い合わせフォームからお送りください。

利用許諾に関するお問い合わせ

本書の書影(表紙画像)をご利用になりたい場合は書影許諾申請フォームから申請をお願いいたします。

書影(表紙画像)以外のご利用については、こちらからお問い合わせください。

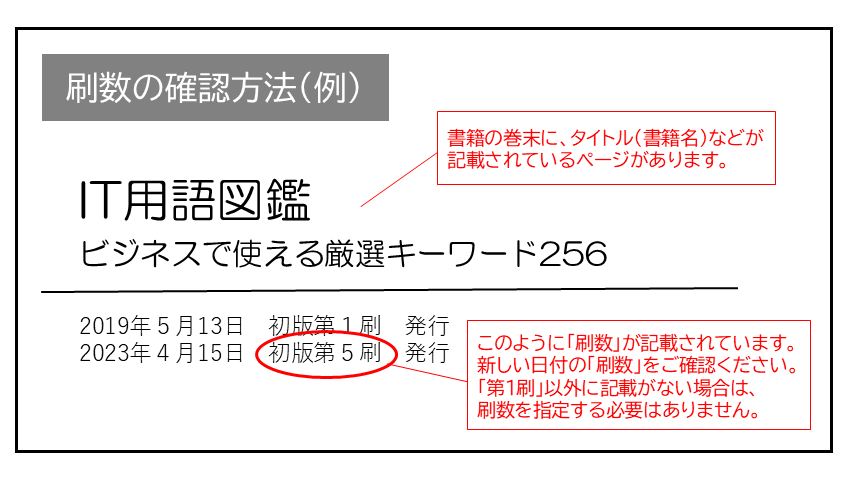

現在表示されている正誤表の対象書籍

書籍の種類:紙書籍

書籍の刷数:全刷

書籍によっては表記が異なる場合がございます

本書に誤りまたは不十分な記述がありました。下記のとおり訂正し、お詫び申し上げます。

対象の書籍は正誤表がありません。

| ページ数 | 内容 | 書籍修正刷 | 電子書籍訂正 | 発生刷 | 登録日 | ||||

|---|---|---|---|---|---|---|---|---|---|

| 031 11行目、12行目 |

|

未 | 未 | 1刷 | 2011.06.13 | ||||

| 091 図5.9 「算術演算」 |

|

2刷 | 未 | 1刷 | 2010.05.19 | ||||

| 221 6行目 |

|

2刷 | 未 | 1刷 | 2010.05.19 | ||||

| 223 中央あたり |

|

2刷 | 未 | 1刷 | 2010.05.19 | ||||

| 224 9行目 |

|

2刷 | 未 | 1刷 | 2010.05.19 | ||||

| 227 本文 |

|

2刷 | 未 | 1刷 | 2010.05.19 | ||||

| 228 本文下から7行目 |

|

2刷 | 未 | 1刷 | 2010.05.19 | ||||

| 284 15.9 本文3行目、4行目 |

|

2刷 | 未 | 1刷 | 2010.05.19 |

YUJIRO さん

2019-11-05

コストと性能という二律背反を如何に実現するか。コンピュータがどのような設計思想のもとで構築されているかを知ることができる。プログラマはこの設計思想を頭に入れておくことで高速なコードを書くことができる。しかし、長くて難しい本。また機会を見つけて読み直したい。

YUJIRO さん

2020-04-26

コンピュータは詳細レベルを抽象化することで、アプリケーションの作成を容易にする。プログラマは、詳細レベルの動作を理解することで、効率の良いソフトウェア開発ができる。

YUJIRO さん

2020-02-29

プロセッサ、メモリ、入出力装置に着目し、コンピュータのアーキテクチャを説明する。図が少なく文章での説明が多い。とはいえ、アーキテクチャをフェッチ実行サイクルの観点から読み解き、限られたコストで如何に効率よく動作させるかの説明を、メリット、デメリットを提示しながら詳しく説明している。厚くて読むのに苦労するが、また機会を見つけて読み直したい。

.png)