組込みI/Oインタフェース基礎講座

- 形式:

- 書籍

- 発売日:

- 2006年09月04日

- ISBN:

- 9784798111100

- 定価:

- 3,080円(本体2,800円+税10%)

- 仕様:

- B5変・384ページ

- カテゴリ:

- ハードウェア・自作

- キーワード:

- #OS・アプリケーション,#開発環境,#ネットワーク・サーバ・セキュリティ,#システム運用

機器制御の仕組みが実践的に理解できる

本書は、最近の組込みシステム関連書の流れに反し、雑多なI/O処理周りのかなり泥臭い部分をまとめた一冊となりました。それは、組込みシステムのソフトウェアに興味を持たれた方に、実際に機器を動かす仕組みの紹介を通じ、ものづくりや、組込みシステムってこんな感じなんだ、という雰囲気をつかんで頂ければと考えたからです。

本書がこれから組込みシステムのソフトウェア開発者を目指そうとする方の最初の一歩として、少しでもお役に立ちますように。

(まえがき より)

第1章 コンピュータと機器制御

はじめに~組込みシステムの世界へようこそ!

1-1 マイクロプロセッサ事始め

1-2 ソフトウェアを部品として機器に組み込む

1-3 組込みシステムの特徴

1-4 マイコンによる機器制御とは

1-5 センサ

第2章 CPUとI/O

はじめに~ハードウェアエンジニアの話すことが理解できるとは

2-1 CPUアーキテクチャとメモリ参照

2-2 I/Oデバイスのマッピング

2-3 ハードウェア構成とバス

2-4 デジタル回路入門

2-5 様々な回路テクニック~順序回路やトリガ

2-6 同期とクロック

2-7 組込みソフトウェアの特徴

第3章 パラレルI/Oの仕組みと使い方

はじめに~「インタフェース」の奥深さに迫る

3-1 組込みシステムのパラレルI/O

3-2 パラレルポートとハンドシェーク

3-3 ハンドシェークの実装と課題

3-4 マイコン内臓パラレルポート

3-5 汎用パラレルI/Fチップ 8255

3-6 パラレルI/Oのまとめ

第4章 シリアルI/Oの仕組みと使い方

はじめに~「シリアルI/O」の本領と進化とは

4-1 シリアルI/Oの基礎

4-2 ベースバンド伝送とブロードバンド伝送

4-3 組込みシステムのシリアルI/O

4-4 RS-232C準拠シリアルインタフェース

4-5 SPIとFlashメモリインタフェース

4-6 I²Cの概要

4-7 組込みシステムのなかのシリアルI/O

4-8 シリアルI/Oのまとめ

第5章 割込み

はじめに~割込みを制するエンジニアは組込みを制す

5-1 割込みとは何か

5-2 割込みの実装

5-3 ISRの実装と動作

5-4 システムの安定動作と割込み処理

5-5 上手な割込みの使い方

第6章 タイマ

はじめに~タイマこそ組込みシステムに不可欠な技術

6-1 タイマの仕組みと種類

6-2 タイマと割込み処理

6-3 タイマやカウンタの用途

6-4 ソフトウェアタイマ

6-5 タイマの周期とシステムの動作

6-6 タイマのまとめ

第7章 ATAとシリアルATA

はじめに~ATAで接続されるデバイス自身、組込みシステムである

7-1 ATAのバックグラウンド

7-2 ハードディスクの基礎知識

7-3 ディスクの性能

7-4 ATAのハードウェア

7-5 ATAコマンドとATAPIサポート系のコマンド

7-6 工学ドライブ系のATAPIパケットコマンド

7-7 ATAの制御ソフトウェア

7-8 シリアルATAのハードウェア

第8章 I/O処理とOS

はじめに~ハードウェアに詳しいだけでよいなら、ハードウェアの開発者が制御コードを書けば済むこと

8-1 組込みソフトウェアの階層化の道のり

8-2 組込みシステムの規模とI/O処理

8-3 マルチタスクとI/O処理プログラム

8-4 非同期I/O処理

8-5 安全設計の原則

8-6 組込みシステムのセキュリティ

付録A ATAレジスタの詳細と役割

付録B-1 IDENTIFY DEVICE情報/IDENTIFY PACKET DEVICE情報

付録B-2 ATA主要コマンドの詳細

付録C ATAPI光学ドライブ系のコマンド

書籍の購入や、商用利用・教育利用を検討されている法人のお客様はこちら

図書館での貸し出しに関するお問い合わせはよくあるお問い合わせをご確認ください。

利用許諾に関するお問い合わせ

本書の書影(表紙画像)をご利用になりたい場合は書影許諾申請フォームから申請をお願いいたします。

書影(表紙画像)以外のご利用については、こちらからお問い合わせください。

お問い合わせ

内容についてのお問い合わせは、正誤表、追加情報をご確認後に、お送りいただくようお願いいたします。

正誤表、追加情報に掲載されていない書籍内容へのお問い合わせや

その他書籍に関するお問い合わせは、書籍のお問い合わせフォームからお送りください。

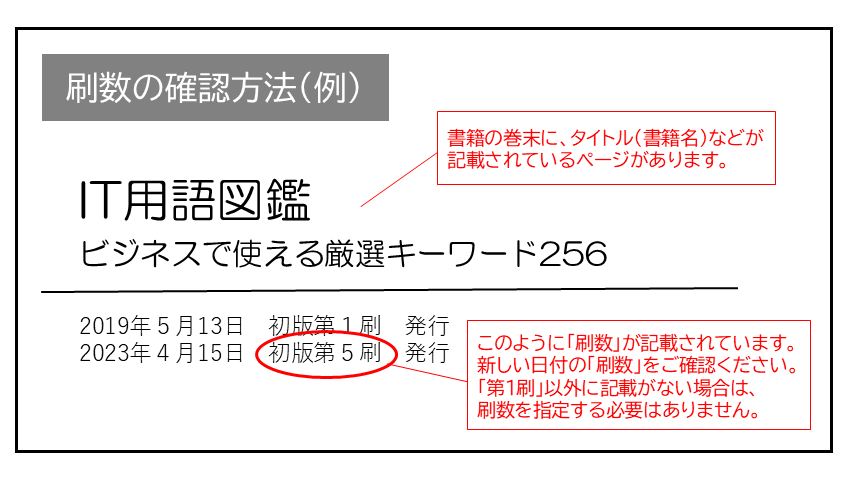

現在表示されている正誤表の対象書籍

書籍の種類:紙書籍

書籍の刷数:全刷

書籍によっては表記が異なる場合がございます

本書に誤りまたは不十分な記述がありました。下記のとおり訂正し、お詫び申し上げます。

対象の書籍は正誤表がありません。

| ページ数 | 内容 | 書籍修正刷 | 電子書籍訂正 | 発生刷 | 登録日 | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| 004 12行目 |

|

2刷 | 未 | 1刷 | 2006.10.26 | ||||||

| 059 図2-26上部の真理値表 |

|

3刷 | 未 | 2刷 | 2011.03.08 | ||||||

| 079 図3-3 囲み解説内最終行 |

|

2刷 | 未 | 1刷 | 2006.09.11 | ||||||

| 103 3-2-3 ニブルモード本文7行目 |

|

3刷 | 未 | 2刷 | 2009.09.30 | ||||||

| 104 図3-19左側の上から3行目、および下の囲み4行目 |

|

3刷 | 未 | 2刷 | 2009.09.30 | ||||||

| 122 13行目 |

|

2刷 | 未 | 1刷 | 2006.10.26 | ||||||

| 128 6行目 |

|

2刷 | 未 | 1刷 | 2006.09.11 | ||||||

| 153 5行目(ページ中央付近) |

|

2刷 | 未 | 1刷 | 2006.10.26 | ||||||

| 214 図5-11中 |

|

2刷 | 未 | 1刷 | 2006.10.26 | ||||||

| 233 本文下から6行目 |

|

2刷 | 未 | 1刷 | 2006.10.26 | ||||||

| 237 下から5~4行目 |

|

2刷 | 未 | 1刷 | 2006.10.26 | ||||||

| 239 3行目 |

|

2刷 | 未 | 1刷 | 2006.10.26 | ||||||

| 261 下から7行目 |

|

2刷 | 未 | 1刷 | 2006.10.26 |

sherbets さん

2016-09-04

勉強になりました。HW動き、制御方法や注意点など。勿論ざっくりしたところは調べて補完が必要ですが、組み込み基礎勉強には良かったです

.png)