情報処理教科書 テクニカルエンジニア[エンベデッドシステム]2007年度版

2007年4月に実施される情報処理技術者試験の受験対策書。エンベデッドシステム(ES)試験に必要な要素知識をわかりやすく解説。さらに問題演習として、ES試験特有の午前問題から精選した100問と、平成18年度に出題された午後I・午後IIの問題を取り上げる。ハードウェアの苦手なソフトウェア技術者でも無理なく合格圏内に導く、効果的な学習書です。

【本書の特徴】

・-技術解説

午前及び午後に共通して関連する技術内容をまとめました。情報処理技術者試験のほかの試験区分でも出題される、ソフトウェア一般やネットワーク及びセキュリティに関する解説は要点にとどめ、エンベデッド試験特有の技術内容に重点をおきました。

・-午前問題の演習

エンベデッド試験で重視される「コンピュータシステム」の分野について過去問題を精選し、分野別に再構成しました。

・-午後問題の演習

平成18年度の午後問題を取り上げ、解答に必要な考え方を中心に解説しました。

テクニカルエンジニア(エンベデッドシステム)になるには

テクニカルエンジニア(エンベデッドシステム)試験とは

出題傾向と学習方法

受験の手引き

本書の使い方

第1章 ハードウェア

1.1 論理回路

1.1.1 組合せ論理回路

1.1.2 順序論理回路

1.2 カウンタとタイマ

1.2.1 カウンタ

1.2.2 タイマ

1.3 A/D, D/A, PWM, PLL

1.3.1 A/D変換機

1.3.2 D/A変換機

1.3.3 PWM

1.3.4 PLL

1.4 LSI

1.4.1 ASIC

1.4.2 ASSP

1.4.3 LSIの設計手法

1.4.4 フィールドプログラマブルロジック

1.5 メモリ

1.5.1 SRAM

1.5.2 DRAM

1.5.3 SDRAM

1.5.4 その他のメモリ

第2章 CPU/メモリアーキテクチャ

2.1 エンベデッドシステムの基本構成

2.1.1 I/Oアクセス方式

2.1.2 ハーバードアーキテクチャ

2.2 CPUアーキテクチャ

2.2.1 CPU高速化アーキテクチャ

2.2.2 DSP

2.3 バスアーキテクチャ

2.3.1 バスの構成要件

2.3.2 システムバス構成

2.3.3 マルチプロセッサ

2.4 メモリアーキテクチャ

2.4.1 メインメモリの制御

2.4.2 キャッシュメモリ

2.4.3 DMA

2.4.4 特殊メモリ

2.5 割込み制御

2.5.1 割込みの概要と種類

2.5.2 割込みの優先順位と多重割込み

2.5.3 割込みコントローラ

第3章 入出力装置

3.1 インタフェース技術

3.1.1 シリアルインタフェース

3.1.2 パラレルインタフェース

3.1.3 高速シリアルインタフェース

3.1.4 無線インタフェース

3.2 代表的な入出力装置

3.2.1 温度センサ

3.2.2 エンコーダ

3.2.3 スイッチ

3.2.4 光学式装置

3.2.5 アクチュエータ

3.2.6 表示装置

第4章 ネットワークとセキュリティ

4.1 ネットワークアーキテクチャ

4.1.1 OSI基本参照モデル

4.1.2 LANのトポロジ

4.1.3 LANのアクセス制御方式

4.2 符号化と伝送

4.2.1 変調・符号化

4.2.2 誤り制御

4.2.3 伝送制御

4.3 電気通信のサービスと関連規格

4.3.1 電気通信サービス

4.3.2 ネットワーク関連の規格

4.4 通信機器

4.4.1 伝送媒体・通信ケーブル

4.4.2 通信装置

4.5 セキュリティ技術

4.5.1 暗号化方式

4.5.2 ディジタル署名

4.5.3 セキュリティ対策技術

4.6 セキュリティマネジメント

4.6.1 情報セキュリティマネジメントシステム

4.6.2 プライバシーマーク

第5章 リアルタイムOS

5.1 リアルタイムOSの特徴と構成

5.1.1 リアルタイムOSの特徴

5.1.2 リアルタイムOSの構成

5.2 タスク管理

5.2.1 タスクの状態遷移

5.2.2 タスクのスケジューリング

5.3 同期制御

5.3.1 同期制御の代表的なメカニズム

5.4 優先度の逆転とデッドロック

5.4.1 優先度の逆転

5.4.2 デッドロック

5.5 性能指標

5.5.1 性能の基準

第6章 要求分析とシステム設計

6.1 要求分析

6.1.1 要求分析

6.1.2 トレードオフ問題

6.1.3 処理速度及びデータ容量の見積り

6.1.4 データの圧縮方式

6.2 システム設計

6.2.1 システム設計

6.2.2 セキュリティ設計

6.2.3 省電力設計

6.2.4 安全性設計

第7章 ソフトウェアの開発

7.1 開発環境と開発手法

7.1.1 言語

7.1.2 開発・デバッグ環境

7.1.3 開発手法

7.2 要求分析・設計手法

7.2.1 要求分析手法

7.2.2 設計手法

7.3 テスト・レビューの手法

7.3.1 テスト手法

7.3.2 レビュー手法

7.4 開発管理

7.4.1 開発管理用ダイアグラム

第8章 午前問題の演習

8.1 情報素子

8.2 プロセッサの構造と動作原理

8.3 プロセッサの高速化技法

8.4 プロセッサの性能

8.5 メモリアーキテクチャ

8.6 補助記憶

8.7 入出力アーキテクチャと装置

8.8 論理回路・信号回路

8.9 制御理論

8.10 A/D変換・D/A変換

8.11 エンコーダ

8.12 モータ

8.13 誤動作対策

8.14 仮想記憶

8.15 プロセス制御・スケジューリング

8.16 排他制御

8.17 システムの性能

8.18 システムの信頼性

第9章 午後問題の演習~ソフトウェア系~

午後 I 演習(1) 排水ポンプの自動運転制御(H18-I-1)

解答・解説

午後 I 演習(2) 複合機(H18-I-3)

解答・解説

午後 II 演習(1) マイコン内蔵型電動リール(H18-II-2)

解答・解説

第10章 午後問題の演習~ハードウェア系~

午後 I 演習(1) 踏切制御装置の設計(H18-I-2)

解答・解説

午後 I 演習(2) 路線バスの車内に設置される総合案内システム(H18-I-4)

解答・解説

午後 II 演習(1) 鋼材切断システムの制御(H18-II-1)

解答・解説

参考資料

お問い合わせ

内容についてのお問い合わせは、正誤表、追加情報をご確認後に、お送りいただくようお願いいたします。

正誤表、追加情報に掲載されていない書籍内容へのお問い合わせや

その他書籍に関するお問い合わせは、書籍のお問い合わせフォームからお送りください。

利用許諾に関するお問い合わせ

本書の書影(表紙画像)をご利用になりたい場合は書影許諾申請フォームから申請をお願いいたします。

書影(表紙画像)以外のご利用については、こちらからお問い合わせください。

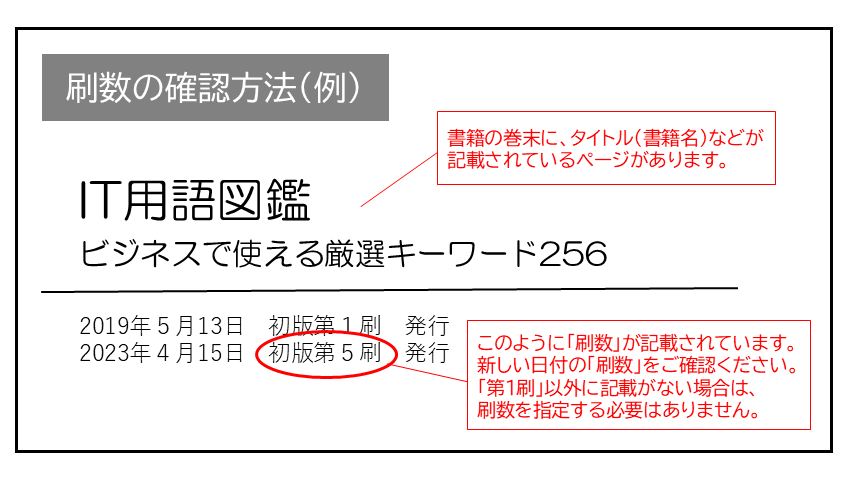

現在表示されている正誤表の対象書籍

書籍の種類:紙書籍

書籍の刷数:全刷

書籍によっては表記が異なる場合がございます

本書に誤りまたは不十分な記述がありました。下記のとおり訂正し、お詫び申し上げます。

対象の書籍は正誤表がありません。

| ページ数 | 内容 | 書籍修正刷 | 電子書籍訂正 | 発生刷 | 登録日 | ||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 005 図:トライステートバッファ |

|

2刷 | 未 | 1刷 | 2006.10.17 | ||||||||||||||||||||||||||||||||||

| 019 図:PLLの構成図 |

|

3刷 | 未 | 2刷 | 2007.01.17 | ||||||||||||||||||||||||||||||||||

| 221 問23の図 |

|

2刷 | 未 | 1刷 | 2006.10.12 | ||||||||||||||||||||||||||||||||||

| 243 下から2行目 |

|

2刷 | 未 | 1刷 | 2006.11.30 | ||||||||||||||||||||||||||||||||||

| 243 解説中の図、および下から7行目 |

|

3刷 | 未 | 2刷 | 2007.01.17 | ||||||||||||||||||||||||||||||||||

| 388 左列、「ト」の8行上 |

|

3刷 | 未 | 2刷 | 2007.01.17 |

.png)