VHDLデジタル回路設計 標準講座

宇野 俊夫 監修

有限会社ハラパン・メディアテック 監修

有限会社ハラパン・メディアテック 翻訳

有限会社ハラパン・メディアテック 原著

宇野 みれ 翻訳

宇野 みれ 原著

Mark Zwolinski 著

- 形式:

- 書籍

- 発売日:

- 2007年05月21日

- ISBN:

- 9784798113852

- 定価:

- 4,180円(本体3,800円+税10%)

- 仕様:

- B5変・408ページ

- カテゴリ:

- ハードウェア・自作

- キーワード:

- #OS・アプリケーション,#開発環境,#ネットワーク・サーバ・セキュリティ,#システム運用

回路設計に携わるすべてのエンジニアに

本書の初版が出版された当時、デジタル回路設計に関するテキストとVHDLのテキストを組み合わせるというアイデアは画期的でした。時を同じくして同じテーマの類書がいくつか出版されました。本書はいくつかの大学で中心的な教科書として採用されました。さらに初版はポーランド語に訳され、台湾向けの廉価版も作成されました。この成功と競争力で、このアイデアが正しいものであったと確信しましたが、初版では完璧を期すことができたとは思えません。この2版は初版で修正すべき点を修正し、さらに2つの重要なトピックを追加しています。(著者まえがきより)

第1章 はじめに

1.1 最新のデジタル回路設計

1.2 CMOSテクノロジ

1.3 プログラマブルロジック

1.4 電気的特性

まとめ/参考文献/練習問題

第2章 組合せ論理回路の設計

2.1 ブール代数

2.2 論理ゲート

2.3 組合せ論理回路の設計

2.4 タイミング

2.5 数字コード

まとめ/参考文献/練習問題

第3章 VHDLゲートモデルを使った組合せ論理回路

3.1 エンティティとアーキテクチャ

3.2 識別子、スペース、コメント

3.3 ネットリスト

3.4 信号割当て

3.5 ジェネリック文

3.6 定数とオープンポート

3.7 テストベンチ

3.8 構成

まとめ/参考文献/練習問題

第4章 組合せ論理回路のビルディングブロック

4.1 トライステートバッファ

4.2 デコーダ

4.3 マルチプレクサ

4.4 プライオリティエンコーダ

4.5 加算器

4.6 パリティチェッカー

4.7 組合せブロックのためのテストベンチ

まとめ/参考文献/練習問題

第5章 同期式順序回路の設計

5.1 同期式順序回路システム

5.2 同期式順序回路システムのモデル

5.3 ASM:アルゴリズム状態マシン

5.4 ASMチャートからの合成

5.5 VHDLにおけるステートマシン

5.6 ステートマシン用のVHDLテストベンチ

まとめ/参考文献/練習問題

第6章 順序回路の論理ブロックのVHDLモデル

6.1 ラッチ

6.2 フリップフロップ

6.3 JKおよびTフリップフロップ

6.4 レジスタとシフトレジスタ

6.5 カウンタ

6.6 メモリ

6.7 シーケンシャル乗算器

6.8 順序回路のビルディングブロックのテストベンチ

まとめ/参考文献/練習問題

第7章 複雑なシーケンシャルシステム

7.1 リンクされたステートマシン

7.2 データパス/コントローラのパーティショニング

7.3 命令

7.4 シンプルなマイクロプロセッサ

7.5 シンプルなマイクロプロセッサのVHDLモデル

まとめ/参考文献/練習問題

第8章 VHDLのシミュレーション

8.1 イベントドリブンのシミュレーション

8.2 VHDLモデルのシミュレーション

8.3 シミュレーションのモデリング問題

8.4 ファイル操作

まとめ/参考文献/練習問題

第9章 VHDLによる論理合成

9.1 RTLの合成

9.2 制約

9.3 FPGAの合成

9.4 ビヘイビア的な合成

9.5 合成結果の検証

まとめ/参考文献/練習問題

第10章 デジタルシステムのテスト

10.1 テストの必要性

10.2 障害モデル

10.3 障害指向のテストパターン生成

10.4 障害シミュレーション

10.5 VHDLにおける障害シミュレーション

まとめ/参考文献/練習問題

第11章 テスト性を高めるための設計

11.1 アドホックテスト性の改善

11.2 テストのための構造化設計

11.3 ビルトイン・セルフテスト

11.4 バウンダリスキャン(IEEE 1149.1)

まとめ/参考文献/練習問題

第12章 非同期方式順序回路の設計

12.1 非同期式回路

12.2 非同期式回路の分析

12.3 非同期式順序回路の設計

12.4 非同期式ステートマシン

12.5 セットアップ/ホールドタイム、メタスタビリティ

まとめ/参考文献/練習問題

第13章 アナログとのインタフェース

13.1 デジタル・アナログコンバータ

13.2 アナログ・デジタルコンバータ

13.3 VHDL-AMS

13.4 PLL

13.5 VHDL-AMSシミュレータ

まとめ/参考文献/練習問題

付録

お問い合わせ

内容についてのお問い合わせは、正誤表、追加情報をご確認後に、お送りいただくようお願いいたします。

正誤表、追加情報に掲載されていない書籍内容へのお問い合わせや

その他書籍に関するお問い合わせは、書籍のお問い合わせフォームからお送りください。

利用許諾に関するお問い合わせ

本書の書影(表紙画像)をご利用になりたい場合は書影許諾申請フォームから申請をお願いいたします。

書影(表紙画像)以外のご利用については、こちらからお問い合わせください。

現在表示されている正誤表の対象書籍

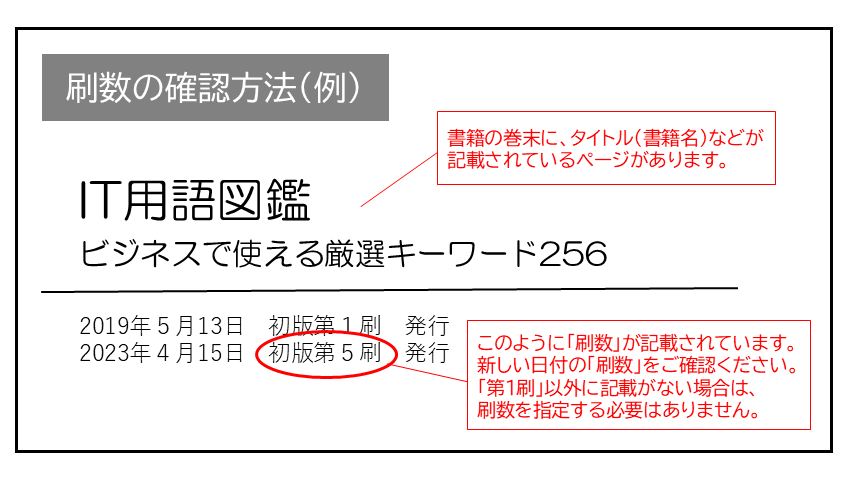

書籍の種類:紙書籍

書籍の刷数:全刷

書籍によっては表記が異なる場合がございます

本書に誤りまたは不十分な記述がありました。下記のとおり訂正し、お詫び申し上げます。

対象の書籍は正誤表がありません。

| ページ数 | 内容 | 書籍修正刷 | 電子書籍訂正 | 発生刷 | 登録日 | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| 051 リストの1つめ 1行目 |

|

未 | 未 | 1刷 | 2013.11.28 | ||||||

| 057 練習問題 3.5 真理値表中 |

|

未 | 未 | 1刷 | 2013.11.28 | ||||||

| 065 4.2.1 2to4デコーダの真理値表中、 |

|

2刷 | 未 | 1刷 | 2007.11.09 | ||||||

| 068 ページ中ほどのリスト8行目 |

|

2刷 | 未 | 1刷 | 2007.11.09 | ||||||

| 070 ページ上部のリストの後2行目 |

|

2刷 | 未 | 1刷 | 2007.11.09 | ||||||

| 071 本文11行目 |

|

2刷 | 未 | 1刷 | 2007.11.09 | ||||||

| 079 本文4行目 |

|

2刷 | 未 | 1刷 | 2007.11.09 | ||||||

| 105 図5.19 シーケンス検出器のASMチャート |

|

2刷 | 未 | 1刷 | 2007.11.09 | ||||||

| 106 1行目数式 |

|

2刷 | 未 | 1刷 | 2007.11.09 | ||||||

| 107 ページ下方の数式(1行目) |

|

2刷 | 未 | 1刷 | 2007.11.09 | ||||||

| 111 本文5行目 |

|

2刷 | 未 | 1刷 | 2007.11.09 | ||||||

| 138 下から3行目 |

|

2刷 | 未 | 1刷 | 2010.01.08 | ||||||

| 144 ページ下部の図 |

|

2刷 | 未 | 1刷 | 2010.07.09 | ||||||

| 252 本文 下から3行目 |

|

未 | 未 | 1刷 | 2014.08.28 | ||||||

| 259 本文 3~4行目 |

|

未 | 未 | 1刷 | 2014.08.28 | ||||||

| 260 本文 下から3~4行目 |

|

未 | 未 | 1刷 | 2014.08.28 | ||||||

| 261 下から5行目 |

|

未 | 未 | 1刷 | 2014.08.28 |

オザマチ さん

2013-02-14

アナログとのインターフェースやシステムのテスト方法まで書いてあるのは珍しいかなぁ。全体的にちょっと難しいと感じました。演習問題・解答つき。

.png)