コンピュータアーキテクチャ定量的アプローチ 第4版

中條 拓伯 監修

中條 拓伯 翻訳

中條 拓伯 原著

John L. Hennessy 著

David A. Patterson 著

天野 英晴 翻訳

天野 英晴 原著

吉瀬 謙二 翻訳

吉瀬 謙二 原著

佐藤 寿倫 翻訳

佐藤 寿倫 原著

- 形式:

- 書籍

- 発売日:

- 2008年02月20日

- ISBN:

- 9784798114408

- 定価:

- 9,020円(本体8,200円+税10%)

- 仕様:

- A5・768ページ

コンピュータアーキテクチャの第一人者が執筆した世界的名著

「RISC」育ての親、ヘネシー&パターソン両教授によるコンピュータアーキテクチャの定番書。初版は1994 年2 月、日経BP 社より刊行され、大ベストセラーになりました。本書はその改訂第4 版を翻訳したものです。姉妹書「コンピュータの構成と設計第3版 上巻・下巻」(日経BP社)はハードウェアからソフトウェアまで網羅した書籍でベストセラーになっています。本書は、CPUアーキテクチャ設計中心にハードウェアにおけるシステムアーキテクチャを詳細に解説。付録のCD-ROMも初邦訳され、さらに学習しやすくなりました。コンピュータの仕組みを学べる定番書として欠かせない一冊です。

1章 計算機設計の基礎

1.1 はじめに

1.2 コンピュータのクラス

1.3 コンピュータアーキテクチャを定義する

1.4 実装テクノロジのトレンド

1.5 半導体の電力のトレンド

1.6 コストのトレンド

1.7 ディペンダビリティ(dependability)

1.8 性能の測定、報告、整理の方法

1.9 計算機設計の定量的な原則

1.10 総合的な実例:性能と価格性能比

1.11 誤った考えと落し穴

1.12 おわりに

1.13 歴史的展望と参照事項

演習問題付きケーススタディ(Diana Franklin)

2章 命令レベル並列性とその活用

2.1 命令レベル並列性:概念とチャレンジ

2.2 命令レベル並列性を見出すための基本的なコンパイラ技術

2.3 予測による分岐コストの削減

2.4 動的スケジューリングによるデータハザードの克服

2.5 動的スケジューリング:例題とアルゴリズム

2.6 ハードウェアベースの投機処理

2.7 多重命令発行と静的スケジューリングを用いた命令レベル並列性の抽出

2.8 動的スケジューリング、多重命令発行および投機処理を用いた命令レベル並列性の抽出

2.9 命令供給と投機処理のための高度な技術

2.10 総合的な実例:Intel Pentium 4

2.11 誤った考えと落し穴

2.12 おわりに

2.13 歴史的展望と参照事項

演習問題付きケーススタディ(Robert P. Colwell)

3章 命令レベル並列性の上限

3.1 はじめに

3.2 ILPの上限

3.3 実現可能なプロセッサでのILPの上限

3.4 他の章との関連:「ハードウェアによる投機」対「ソフトウェアによる投機」

3.5 マルチスレッディング:スレッドレベル並列性抽出のためのILPサポートの利用

3.6 総合的な実例:先端的多重命令発行プロセッサでの性能と効率

3.7 誤った考えと落し穴

3.8 おわりに

3.9 歴史的展望と参照事項

演習問題付きケーススタディ(Wen-mei W. HwuとJohn W. Sias)

4章 マルチプロセッサとスレッドレベル並列性

4.1 はじめに

4.2 対称型共有メモリアーキテクチャ

4.3 対称型共有メモリマルチプロセッサの性能

4.4 分散共有メモリとディレクトリベースコヒーレンス制御

4.5 同期:その基本

4.6 メモリコンシステンシモデル:導入

4.7 他の章との関連

4.8 総合的な実例:Sun T1マルチプロセッサ

4.9 誤った考えと落し穴

4.10 おわりに

4.11 歴史的展望と参照事項

演習問題付きケーススタディ(David A. Wood)

5章 メモリ階層の設計

5.1 はじめに

5.2 キャッシュの性能向上のための11のより進んだ改良法

5.3 メモリ技術と最適化

5.4 保護:仮想記憶と仮想マシン

5.5 他の章との関連:記憶階層の設計

5.6 総合的な実例:AMD Opteronの記憶階層

5.7 誤った考えと落し穴

5.8 おわりに

5.9 歴史的展望と参照事項

演習問題付きケーススタディ(Norman P. Jouppi)

6章 ストレージシステム

6.1 はじめに

6.2 ディスク記憶装置の最近の動向

6.3 実際の欠陥と障害の定義と例

6.4 I/O性能、信頼性の測定およびベンチマーク

6.5 待ち行列理論入門

6.6 他の章との関連

6.7 I/Oシステムの設計と評価:インターネットアーカイブクラスタの例

6.8 総合的な実例:NetApp FAS6000ファイラ

6.9 誤った考えと落し穴

6.10 おわりに

6.11 歴史的展望と参照事項

演習問題付きケーススタディ(Andrea C. Arpaci-Dusseau、Remzi H. Arpaci-Dusseau)

付録 A パイプライン処理:基本および中間的な概念

A.1 はじめに

A.2 パイプライン処理の主要な障害:パイプラインハザード

A.3 パイプラインの実装法

A.4 何がパイプラインの実装を困難にするのだろう?

A.5 複数サイクル演算を扱うためのMIPSパイプライン拡張

A.6 総合的な実例:MIPS R4000パイプライン

A.7 他の章との関連

A.8 誤った考えと落し穴

A.9 おわりに

A.10 歴史的展望と参照事項

付録 B 命令セットの原理と例

B.1 はじめに

B.2 命令セットアーキテクチャの分類

B.3 メモリアドレッシング

B.4 オペランドタイプとオペランドサイズ

B.5 命令セットにおける命令操作

B.6 制御のための命令

B.7 命令セットのエンコード

B.8 他の章との関連:コンパイラの役割

B.9 他の章との関連:MIPSアーキテクチャ

B.10 誤った考えと落し穴

B.11 おわりに

B.12 歴史的展望と参照事項

付録 C 記憶階層の復習

C.1 はじめに

C.2 キャッシュの性能

C.3 6つの基本的なキャッシュ改良法

C.4 仮想記憶

C.5 仮想記憶の保護とその例

C.6 誤った考えと落し穴

C.7 おわりに

C.8 歴史的展望と参照事項

CD-ROM収録付録

付録 D 組み込みシステム

付録 E 相互結合網

付録 F ベクトルプロセッサ

付録 G VLIW・EPIC向けハードウェアとソフトウェア

付録 H 大規模マルチプロセッサと科学技術アプリケーション

付録 I コンピュータの演算法

付録 J さまざまな命令セットアーキテクチャ

付録 K 歴史的視点と参考文献

書籍の購入や、商用利用・教育利用を検討されている法人のお客様はこちら

図書館での貸し出しに関するお問い合わせはよくあるお問い合わせをご確認ください。

利用許諾に関するお問い合わせ

本書の書影(表紙画像)をご利用になりたい場合は書影許諾申請フォームから申請をお願いいたします。

書影(表紙画像)以外のご利用については、こちらからお問い合わせください。

お問い合わせ

内容についてのお問い合わせは、正誤表、追加情報をご確認後に、お送りいただくようお願いいたします。

正誤表、追加情報に掲載されていない書籍内容へのお問い合わせや

その他書籍に関するお問い合わせは、書籍のお問い合わせフォームからお送りください。

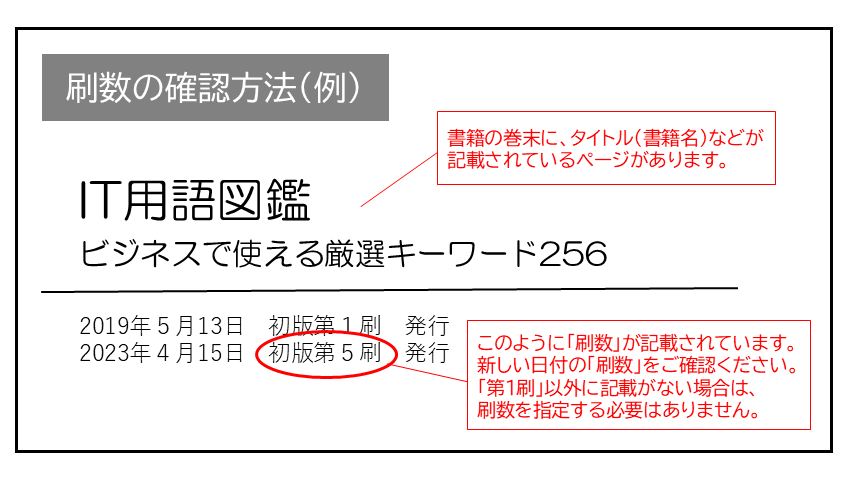

現在表示されている正誤表の対象書籍

書籍の種類:紙書籍

書籍の刷数:全刷

書籍によっては表記が異なる場合がございます

本書に誤りまたは不十分な記述がありました。下記のとおり訂正し、お詫び申し上げます。

対象の書籍は正誤表がありません。

| ページ数 | 内容 | 書籍修正刷 | 電子書籍訂正 | 発生刷 | 登録日 | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| 002 2行目 |

|

未 | 未 | 1刷 | 2011.06.01 | ||||||

| 010 「2. メモリアドレス」5行目 |

|

未 | 未 | 1刷 | 2011.06.01 | ||||||

| 012 浮動小数点 「SUB.D、SUB.S、SUB.PS」の「命令の意味」 |

|

未 | 未 | 1刷 | 2011.06.16 | ||||||

| 025 8行目 |

|

未 | 未 | 1刷 | 2011.06.16 | ||||||

| 027 下から3行目 |

|

未 | 未 | 1刷 | 2011.06.16 | ||||||

| 036 式 |

|

未 | 未 | 1刷 | 2011.06.16 | ||||||

| 037 例題1.6 1行目 |

|

未 | 未 | 1刷 | 2011.06.16 | ||||||

| 053 「誤った考え」2つ目 1行目 |

|

未 | 未 | 1刷 | 2011.06.16 | ||||||

| 056 14行目 |

|

未 | 未 | 1刷 | 2011.06.16 | ||||||

| 064 ■の5つ目 |

|

未 | 未 | 1刷 | 2011.06.16 | ||||||

| 065 1.13 |

|

未 | 未 | 1刷 | 2011.06.16 | ||||||

| 101 図のキャプション 最終行 |

|

未 | 未 | 1刷 | 2011.06.16 | ||||||

| 105 図2.10 リザベーションステーション Load2のA |

|

2刷 | 未 | 1刷 | 2008.04.22 | ||||||

| 105 図2.10 リザベーションステーション Add1のVk |

|

2刷 | 未 | 1刷 | 2008.04.22 | ||||||

| 105 図2.10 リザベーションステーション Mult2のVk |

|

2刷 | 未 | 1刷 | 2008.04.22 | ||||||

| 107 図2.11 リザベーションステーション Mult1のVj |

|

2刷 | 未 | 1刷 | 2008.04.22 | ||||||

| 107 図2.11 リザベーションステーション Mult2のVk |

|

2刷 | 未 | 1刷 | 2008.04.22 | ||||||

| 108 図2.12 「リザベーションステーションrが空」の「動作および管理情報の更新作業」4行目 |

|

2刷 | 未 | 1刷 | 2009.07.10 | ||||||

| 111 下から9行目 |

|

未 | 未 | 1刷 | 2011.06.01 | ||||||

| 117 図2.15 「リオーダバッファ」の「状態」 |

|

2刷 | 未 | 1刷 | 2009.07.10 | ||||||

| 131 図2.21 項目 |

|

2刷 | 未 | 1刷 | 2008.04.22 | ||||||

| 131 図2.21 項目 |

|

2刷 | 未 | 1刷 | 2008.04.22 | ||||||

| 134 例題2.11 解答 5行目 |

|

2刷 | 未 | 1刷 | 2009.07.10 | ||||||

| 141 13行目 |

|

未 | 未 | 1刷 | 2011.06.01 | ||||||

| 213 15行目 |

|

2刷 | 未 | 1刷 | 2009.08.18 | ||||||

| 238 8行目 |

|

未 | 未 | 1刷 | 2011.06.17 | ||||||

| 258 「4.5 同期:その基本」4~5行目 |

|

未 | 未 | 1刷 | 2011.06.17 | ||||||

| 260 8行目 |

|

2刷 | 未 | 1刷 | 2011.06.17 | ||||||

| 274 T1の性能 |

|

未 | 未 | 1刷 | 2011.06.17 | ||||||

| 276 下から2行目 |

|

未 | 未 | 1刷 | 2011.06.17 | ||||||

| 277 4~5行目 |

|

未 | 未 | 1刷 | 2011.06.17 | ||||||

| 278 図のキャプション 2行目 |

|

未 | 未 | 1刷 | 2011.06.17 | ||||||

| 284 下から5行目 |

|

2刷 | 未 | 1刷 | 2011.06.17 | ||||||

| 285 誤った考え |

|

未 | 未 | 1刷 | 2011.06.10 | ||||||

| 300 下から10行目 |

|

2刷 | 未 | 1刷 | 2011.06.17 | ||||||

| 326 図5.10 |

|

未 | 未 | 1刷 | 2012.01.04 | ||||||

| 329 図のキャプション 2行目 |

|

未 | 未 | 1刷 | 2011.06.17 | ||||||

| 334 図の下の本文 5行目 |

|

未 | 未 | 1刷 | 2011.06.17 | ||||||

| 336 図5.10 |

|

未 | 未 | 1刷 | 2012.01.04 | ||||||

| 345 「DRAMチップ内のメモリ性能の改善」8行目 |

|

未 | 未 | 1刷 | 2011.06.17 | ||||||

| 352 下から2行目 |

|

未 | 未 | 1刷 | 2011.06.01 | ||||||

| 354 ページ最終行 |

|

未 | 未 | 1刷 | 2012.01.04 | ||||||

| 354 下から14行目 |

|

未 | 未 | 1刷 | 2011.06.17 | ||||||

| 369 表の項目名「Opteron」 |

|

未 | 未 | 1刷 | 2011.06.17 | ||||||

| 382 コード3行目 |

|

未 | 未 | 1刷 | 2011.06.17 | ||||||

| 408 2つめの■ 3行目 |

|

未 | 未 | 1刷 | 2011.06.01 | ||||||

| 427 9行目 |

|

未 | 未 | 1刷 | 2011.06.17 | ||||||

| 429 例題6.2 解説 最後の式 |

|

未 | 未 | 1刷 | 2011.06.17 | ||||||

| 471 13行目 |

|

未 | 未 | 1刷 | 2011.06.16 | ||||||

| 477 14行目 |

|

未 | 未 | 1刷 | 2011.06.01 | ||||||

| 483 本文6行目、最終行 |

|

未 | 未 | 1刷 | 2011.06.01 | ||||||

| 550 12行目 |

|

未 | 未 | 1刷 | 2011.06.16 | ||||||

| 582 「手続き呼び出しにおける選択肢」最終行 |

|

未 | 未 | 1刷 | 2011.06.16 | ||||||

| 597 ■の3つ目 |

|

未 | 未 | 1刷 | 2011.06.16 | ||||||

| 600 最終行 |

|

未 | 未 | 1刷 | 2011.06.16 | ||||||

| 604 浮動小数点 「SUB.D、SUB.S、SUB.PS」の「命令の意味」 |

|

未 | 未 | 1刷 | 2011.06.16 | ||||||

| 621 「記憶階層における4つの問い」3行目 |

|

未 | 未 | 1刷 | 2011.06.16 | ||||||

| 627 例題C.3 |

|

2刷 | 未 | 1刷 | 2009.08.18 | ||||||

| 627 例題C.3 2行目 |

|

未 | 未 | 1刷 | 2011.06.16 | ||||||

| 633 6行目 |

|

未 | 未 | 1刷 | 2011.06.16 | ||||||

| 634 例題C.5 解答 3行目 |

|

2刷 | 未 | 1刷 | 2009.08.18 | ||||||

| 635 4行目 |

|

未 | 未 | 1刷 | 2011.06.16 | ||||||

| 636 11~12行目 |

|

2刷 | 未 | 1刷 | 2009.08.18 | ||||||

| 636 7行目 |

|

未 | 未 | 1刷 | 2011.06.16 | ||||||

| 637 本文1行目 |

|

未 | 未 | 1刷 | 2012.01.04 | ||||||

| 639 最後の式 一番右側の項 |

|

未 | 未 | 1刷 | 2011.06.16 | ||||||

| 645 図C.12 |

|

2刷 | 未 | 1刷 | 2009.08.18 | ||||||

| 646 2行目 |

|

2刷 | 未 | 1刷 | 2009.08.18 | ||||||

| 649 最終行の式 一番右側の項 |

|

未 | 未 | 1刷 | 2011.06.16 | ||||||

| 650 下から9行目 |

|

未 | 未 | 1刷 | 2011.06.16 | ||||||

| 658 下から8~7行目 |

|

未 | 未 | 1刷 | 2011.06.16 | ||||||

| 664 4行目 |

|

未 | 未 | 1刷 | 2011.06.16 | ||||||

| 727 下から7行目 |

|

未 | 未 | 1刷 | 2011.06.16 | ||||||

| vi 8行目 |

|

未 | 未 | 1刷 | 2011.06.01 | ||||||

| xv 2行目 |

|

未 | 未 | 1刷 | 2011.06.01 | ||||||

| xvii 謝辞 2行目 |

|

未 | 未 | 1刷 | 2011.06.16 | ||||||

| 表紙裏 「11」下から2行目 |

|

未 | 未 | 1刷 | 2011.06.16 | ||||||

| 裏表紙の裏 浮動小数点 「SUB.D、SUB.S、SUB.PS」の「命令の意味」 |

|

未 | 未 | 1刷 | 2011.06.16 |

kaizen@名古屋de朝活読書会 さん

2012-09-26

C言語の移植性を考えるためコンピュータのアーキテクチャを勉強。「コンピュータの設計と構成」と併読む。付録Bにコンパイラに関連する命令セットの話。インテルの成功の理由を3つ。1初期のIBM PCで採用。バイナリ互換が重要。2十分なハードウェア資源が利用でき80x86命令を内部でRISC命令セットに飜訳しRISCライクな命令を実行。3PCマイクロプロセッサは市場規模が非常に大き井。ハードウェアによるRISC命令への返還に要する設計費用が増加しても容易に償却。製品の費用を低下。

fjt7tdmi さん

コンピュータアーキテクチャに興味がある人は読んでおいた方が良い一冊、それ以外の人はここまでの知識は必要なという一冊。 私が最初にこの本を読んだ時点では第4版だったのだが、最新の第6版で大きく更新されており、RISCV やら DSA やら流行りの内容を扱うようになった。 これから読む人は、最新版だけ読むのが良いだろう。