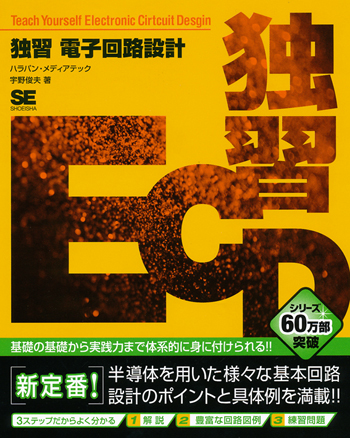

独習 電子回路設計

宇野 俊夫 著

- 形式:

- 書籍

- 発売日:

- 2010年01月28日

- ISBN:

- 9784798119755

- 定価:

- 3,740円(本体3,400円+税10%)

- 仕様:

- B5変・544ページ

- シリーズ:

- 独習

好評新定番『独習 電気/電子工学』に続くステップ登場!

本書は電子回路の設計に必要な実践的な技術を身につけたい方に向けて、独習書として構成されています。電子工学系の学生諸子はもちろん、既に技術者として活躍中の方がステップアップを目指すためにも役立つよう配慮しました。実際、本書に掲載された回路図は、一部の概念図を除きすべて動作確認済みで、周波数特性図や波形、ロジック出力等は実物やシミュレータの出力結果です。(中略)フリーで入手できるSpiceベースの回路シミュレータやVHDL開発ツール/シミュレータを利用し、本書の回路を実際に入力して動作を確かめながら読み進めて行けば、飛躍的に理解を深めることができるでしょう。

第1章 ダイオードとトランジスタ

ダイオードの概要

トランジスタの概要

トランジスタの動作点とバイアス回路

電界効果トランジスタ(FET)の概要

第1章のテスト

第2章 電源回路の仕組みと実用設計

電源回路の概要

簡単なシリーズ電源の設計

電流ブースター回路

可変電圧出力回路の設計

保護回路

CVCC(定電圧低電流)電源

三端子レギュレータを使った電源回路

スイッチングレギュレータの仕組み

DC-DCコンバータ

第2章のテスト

第3章 低周波増幅回路

増幅回路の種類と原理

小信号低周波増幅回路の設計

高利得増幅回路の基礎原理

高利得増幅回路と負帰還増幅回路

負帰還増幅回路の設計

エミッタフォロワ

SEPP・・・バッファアンプ

ダーリントン接続回路

電力増幅回路

A級増幅回路の設計

B級プッシュプル増幅回路

AB級プッシュプル増幅回路

コンプリメンタリ回路

DCアンプと差動増幅回路

カレントミラー回路

第3章のテスト

第4章 オペアンプ

オペアンプの概要

オペアンプの基本

オペアンプの増幅率

カスケード接続

差動増幅回路

ボルテージフォロワ

オペアンプの増幅度と周波数特性

演算回路

様々なオペアンプ応用回路

第4章のテスト

第5章 低周波発振回路

発振の仕組み

信号波形

矩形波発振回路

CR正弦波発振回路

三角波発振回路

のこぎり波発振回路

VCO:電圧制御発振器

単安定マルチバイブレータ

きれいな正弦波を得る工夫

第5章のテスト

第6章 フィルタ回路

フィルタの概要

パッシブ・バタワースフィルタ

LCRバタワースフィルタ

正規化フィルタのLPFからHPFへの変換

ベッセルフィルタ

チェビシェフフィルタ

アクティブフィルタ

高次アクティブフィルタ

第6章のテスト

第7章 高周波増幅回路

高周波回路の基礎

高周波回路とダイオード

高周波トランジスタ回路

トランジスタで高域特性を伸ばす工夫

カスコード回路

スイッチ回路

ミキサー回路

中和回路

第7章のテスト

第8章 高周波発振回路

高周波発振回路の概要

LC発振回路の設計

コルビッツ発振回路

コルビッツ発振回路の設計例

ハートレー発振回路

水晶発振回路

トランジスタによる水晶発振回路

オーバートーン発振回路

デジタルICによる水晶発振回路

CMOSオーバートーン水晶発振回路

デジタルICによる水晶発振回路の動作チェック

第8章のテスト

第9章 デジタル回路の基礎

デジタル回路の考え方

基本倫理回路

基本倫理回路の実装~標準ロジックIC

デジタル回路と時間

デジタル回路と電源

第9章のテスト

第10章 組合せ倫理回路

組合せ倫理回路のビルディングブロック

回路の正論理と負論理

高機能な組合せ倫理回路と回路図記号

ハザード

第10章のテスト

第11章 順序回路

順序回路とは

フリップフロップ

フリップフロップの設定端子とタイミング

順序回路の応用

同期回路/非同期回路

第11章のテスト

第12章 有限状態マシン

有限状態マシン

順序回路と状態マシン

状態遷移図と回路設計

ソフトウェアとハードウェア

第12章のテスト

第13章 HDLによるデジタル回路設計

VHDLの概要

VHDLのキー・コンセプト

VHDLの基本文法

組合せ倫理回路の便利な記述法

順序回路の記述

変数と定数

アトリビュート

VHDLによる組合せ倫理回路の記述

VHDLによる順序回路の記述

VHDLの階層設計

メモリの記述

VHDLによる状態マシンの記述

第13章のテスト

付属データはこちら

お問い合わせ

内容についてのお問い合わせは、正誤表、追加情報をご確認後に、お送りいただくようお願いいたします。

正誤表、追加情報に掲載されていない書籍内容へのお問い合わせや

その他書籍に関するお問い合わせは、書籍のお問い合わせフォームからお送りください。

利用許諾に関するお問い合わせ

本書の書影(表紙画像)をご利用になりたい場合は書影許諾申請フォームから申請をお願いいたします。

書影(表紙画像)以外のご利用については、こちらからお問い合わせください。

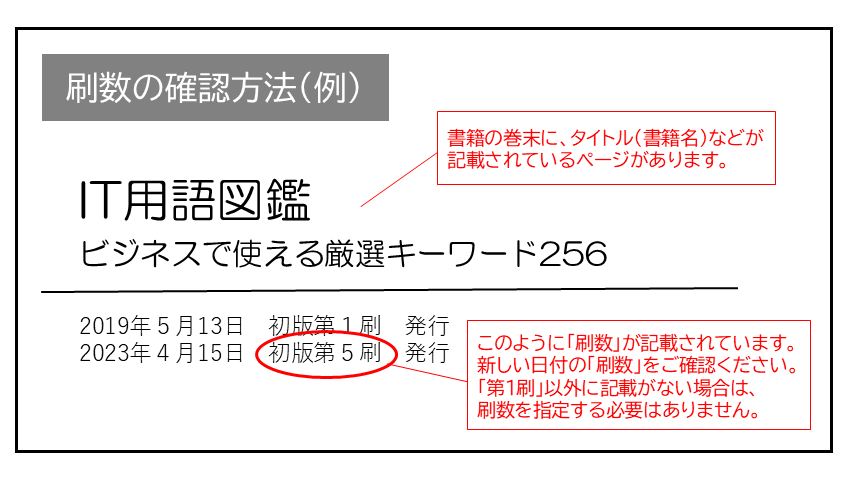

現在表示されている正誤表の対象書籍

書籍の種類:紙書籍

書籍の刷数:全刷

書籍によっては表記が異なる場合がございます

本書に誤りまたは不十分な記述がありました。下記のとおり訂正し、お詫び申し上げます。

対象の書籍は正誤表がありません。

| ページ数 | 内容 | 書籍修正刷 | 電子書籍訂正 | 発生刷 | 登録日 | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| 002 図1-1 右側のブリッジダイオードの図 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 003 図1-2のキャプション 最終行 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 004 図1-3 凡例 |

|

未 | 未 | 1刷 | 2012.02.03 | ||||||

| 006 図1-5 グラフの横軸キャプション |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 010 「チェック」の見出し |

|

未 | 未 | 1刷 | 2013.08.27 | ||||||

| 010 コラム「チェック」 箇条書き第4項「E96系列は…」の2行目 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 015 5~6行目 |

|

未 | 未 | 1刷 | 2013.08.27 | ||||||

| 016 「二次降伏現象」の1行上 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 016 下から2行目 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 017 理解度チェック3)(B) |

|

未 | 未 | 1刷 | 2013.07.05 | ||||||

| 019 式1-1 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 021 「電流帰還バイアス回路の設計の基本」の4行上 |

|

未 | 未 | 1刷 | 2013.08.27 | ||||||

| 021 「電流帰還バイアス回路の設計の基本」の2行上 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 024 式1-6 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 024 式1-7 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 025 6行目 |

|

未 | 未 | 1刷 | 2013.08.27 | ||||||

| 025 1行目 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 032 「FETの回路動作原理」の5行目 |

|

未 | 未 | 1刷 | 2013.08.27 | ||||||

| 033 下から6~5行目 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 036 「FETの品種の検討」の2行上 |

|

未 | 未 | 1刷 | 2013.08.27 | ||||||

| 037 「V DSと電力損失P Dを求める」の1~4行目 |

|

未 | 未 | 1刷 | 2013.08.27 | ||||||

| 039 7行目(式) |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 041 8) 図Ex1-4 R4の値 |

|

未 | 未 | 1刷 | 2013.03.13 | ||||||

| 041 5)の(A) |

|

未 | 未 | 1刷 | 2013.08.27 | ||||||

| 046 「電圧変換回路」の4~5行目 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 046 式2-1 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 048 図2-2 右段、下から3行目 |

|

未 | 未 | 1刷 | 2013.08.27 | ||||||

| 050 「雷サージ対策」の2行上 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 052 下から3行目 |

|

未 | 未 | 1刷 | 2013.08.27 | ||||||

| 052 図2-3 上段のグラフの横軸 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 053 1行目 |

|

未 | 未 | 1刷 | 2013.08.27 | ||||||

| 054 式2-2 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 054 式2-3 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 059 式2-7 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 059 式2-9 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 059-060 p.59の最下行からp.60の4行目まで |

|

未 | 未 | 1刷 | 2013.08.27 | ||||||

| 061 図2-9の左上方 Vinの値 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 062 式2-10の次の行 |

|

未 | 未 | 1刷 | 2013.08.27 | ||||||

| 062 「ブリーダ抵抗の決定」の7行上 |

|

未 | 未 | 1刷 | 2013.08.27 | ||||||

| 062 式2-10 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 063 式2-12 |

|

未 | 未 | 1刷 | 2013.08.27 | ||||||

| 063 式2-14の1行下 |

|

未 | 未 | 1刷 | 2013.08.27 | ||||||

| 064 11行目 |

|

未 | 未 | 1刷 | 2014.07.16 | ||||||

| 065 式2-17 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 066 下から3行目 |

|

未 | 未 | 1刷 | 2013.08.27 | ||||||

| 066 式2-22 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 066-067 p.66の最下行からp.67の4行目まで |

|

未 | 未 | 1刷 | 2013.08.27 | ||||||

| 069 「フォールドバック・カレントリミッター回路」の5行上 |

|

未 | 未 | 1刷 | 2013.08.27 | ||||||

| 069 「カレントリミッター」の8行目 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 070 6~7行目 |

|

未 | 未 | 1刷 | 2010.02.02 | ||||||

| 071 式2-25 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 071 式2-26 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 072 図2-11 図中の抵抗器のリファレンス名称 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 080 式2-32 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 081 式2-34 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 087 図2-22 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 088 最下行 |

|

未 | 未 | 1刷 | 2013.08.27 | ||||||

| 090 2~3行目 |

|

未 | 未 | 1刷 | 2013.08.27 | ||||||

| 091 6行目からの箇条書き |

|

未 | 未 | 1刷 | 2013.07.05 | ||||||

| 094 「理解度チェック」の4行上 |

|

未 | 未 | 1刷 | 2013.08.27 | ||||||

| 099 図3-1 ブリーダ抵抗のリファレンス名称 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 100 式3-7の4行目 |

|

未 | 未 | 1刷 | 2013.08.28 | ||||||

| 101 2行目 |

|

未 | 未 | 1刷 | 2013.08.28 | ||||||

| 101 「式1-6 と1-8 の関係の整理:」の1行目 |

|

未 | 未 | 1刷 | 2013.08.28 | ||||||

| 102 下から6行目 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 103 欄外 注 |

|

未 | 未 | 1刷 | 2010.02.02 | ||||||

| 103 図3-2 Rcの定数(中央上部) |

|

未 | 未 | 1刷 | 2013.06.25 | ||||||

| 104 式3-12 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 104 「入出力インピーダンスの検証」4行上 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 105 本文 下から2行目 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 107 最下行の下 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 107 式の下、本文9行目 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 110 図3-10のキャプション |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 111 図3-13 R3の定数(中ほど上部) |

|

未 | 未 | 1刷 | 2013.06.25 | ||||||

| 113 式3-18 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 114 式3-24の2~1行上 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 115 式3-26の2行目 |

|

未 | 未 | 1刷 | 2013.08.28 | ||||||

| 115 「帰還回路の解析」の6行目 |

|

未 | 未 | 1刷 | 2013.08.28 | ||||||

| 115 式3-26 1行目と2行目の式 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 115 「帰還回路の解析」の2行上 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 115 「帰還回路の解析」5~6行目 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 116 3行目 |

|

未 | 未 | 1刷 | 2013.08.28 | ||||||

| 117 式3-30 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 118 「トランジスタの選択」の5行目 |

|

未 | 未 | 1刷 | 2013.08.28 | ||||||

| 118 図3-15 図中の2つのトランジスタのリファレンス名 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 120 式3-33の4行目 |

|

未 | 未 | 1刷 | 2013.08.28 | ||||||

| 121 「理解度チェック」1)の(B) |

|

未 | 未 | 1刷 | 2013.08.28 | ||||||

| 124 式3-34 左側 |

|

未 | 未 | 1刷 | 2010.02.02 | ||||||

| 125 式3-35 1行目 |

|

未 | 未 | 1刷 | 2010.02.02 | ||||||

| 125 図3-18 定数(4か所) |

|

未 | 未 | 1刷 | 2013.08.28 | ||||||

| 126 最下行 |

|

未 | 未 | 1刷 | 2013.08.28 | ||||||

| 127 図3-21(a)のキャプション |

|

未 | 未 | 1刷 | 2013.08.28 | ||||||

| 127 図3-20のR2の定数 |

|

未 | 未 | 1刷 | 2013.06.25 | ||||||

| 127 図3-21(a)R6の定数 |

|

未 | 未 | 1刷 | 2013.06.25 | ||||||

| 129 「理解度チェック」1)の(A)(B) |

|

未 | 未 | 1刷 | 2013.08.28 | ||||||

| 129 図3-22 参照記号 |

|

未 | 未 | 1刷 | 2013.06.25 | ||||||

| 133 式3-36の右端 |

|

未 | 未 | 1刷 | 2013.08.28 | ||||||

| 134 式3-37から、下から2行目まで |

|

未 | 未 | 1刷 | 2013.08.28 | ||||||

| 134 図3-23 C1とR2の定数 |

|

未 | 未 | 1刷 | 2013.06.25 | ||||||

| 137 式3-39 |

|

未 | 未 | 1刷 | 2013.08.28 | ||||||

| 139 「理解度チェック」5)の(A) |

|

未 | 未 | 1刷 | 2013.08.28 | ||||||

| 140 図3-28 R5とR6の定数 |

|

未 | 未 | 1刷 | 2013.06.25 | ||||||

| 141 下から12行目 |

|

未 | 未 | 1刷 | 2013.08.28 | ||||||

| 142 式3-41の1行目左辺 |

|

未 | 未 | 1刷 | 2013.08.28 | ||||||

| 144 式3-42の1行目 |

|

未 | 未 | 1刷 | 2013.08.28 | ||||||

| 145 式3-44と式3-45の間の本文 |

|

未 | 未 | 1刷 | 2010.02.02 | ||||||

| 145 式3-44 |

|

未 | 未 | 1刷 | 2013.08.28 | ||||||

| 147 図3-34 RE1の定数 |

|

未 | 未 | 1刷 | 2013.06.25 | ||||||

| 148 式3-46の2行目、3行目 |

|

未 | 未 | 1刷 | 2013.08.28 | ||||||

| 148 式3-47の2行目、3行目 |

|

未 | 未 | 1刷 | 2013.08.28 | ||||||

| 148 式3-48 |

|

未 | 未 | 1刷 | 2013.08.28 | ||||||

| 150 「理解度チェック」4)の(E) |

|

未 | 未 | 1刷 | 2013.08.28 | ||||||

| 151 コラム「チェック」の見出し |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 152 「理解度チェック」1)の(C) |

|

未 | 未 | 1刷 | 2013.08.28 | ||||||

| 157 「オペアンプの特徴」の7行目後半 |

|

未 | 未 | 1刷 | 2013.07.05 | ||||||

| 162 図4-2 |

|

未 | 未 | 1刷 | 2013.08.28 | ||||||

| 162 式4-1 6行目の分子 |

|

未 | 未 | 1刷 | 2013.08.28 | ||||||

| 162 式4-2 1行目の分子 |

|

未 | 未 | 1刷 | 2013.08.28 | ||||||

| 162 式4-2 3行目の分子および分母(3か所) |

|

未 | 未 | 1刷 | 2013.08.28 | ||||||

| 162 図4-3 |

|

未 | 未 | 1刷 | 2013.08.28 | ||||||

| 163 「入力抵抗の維持と利得の増大」の16行目 |

|

未 | 未 | 1刷 | 2013.08.28 | ||||||

| 170 式4-8の1行目 |

|

未 | 未 | 1刷 | 2013.08.28 | ||||||

| 174 「様々なオペアンプ応用回路」の2行目 |

|

未 | 未 | 1刷 | 2013.08.28 | ||||||

| 175 図4-18 R1の定数 |

|

未 | 未 | 1刷 | 2013.06.25 | ||||||

| 176 式4-14 2行目 |

|

未 | 未 | 1刷 | 2013.08.28 | ||||||

| 176 式4-14の2行下 |

|

未 | 未 | 1刷 | 2013.08.28 | ||||||

| 177 式4-18の下 |

|

未 | 未 | 1刷 | 2013.08.28 | ||||||

| 178 1行目 |

|

未 | 未 | 1刷 | 2013.08.28 | ||||||

| 179 図4-26 R5の定数 |

|

未 | 未 | 1刷 | 2013.06.25 | ||||||

| 179 図4-24 リファレンスおよび定数 |

|

未 | 未 | 1刷 | 2013.06.25 | ||||||

| 184 図4-37 |

|

未 | 未 | 1刷 | 2013.08.28 | ||||||

| 184 式4-24 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 185 式4-25 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 185 式4-25の5行下 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 186 図Ex4-3 |

|

未 | 未 | 1刷 | 2010.04.21 | ||||||

| 187 図Ex4-4 R3とP1の定数 |

|

未 | 未 | 1刷 | 2013.06.25 | ||||||

| 188 図Ex4-7(E) 各リファレンスとその定数 |

|

未 | 未 | 1刷 | 2013.06.25 | ||||||

| 193 図5-1 キャプション 3行目 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 198 下から3行目 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 199 図5-2 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 199 下から9行目 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 200 式5-1の3行目 |

|

未 | 未 | 1刷 | 2013.08.29 | ||||||

| 205 図5-7 図中のリファレンス番号 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 206 下から15行目 |

|

未 | 未 | 1刷 | 2013.08.29 | ||||||

| 207 図5-9 図中のリファレンス番号 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 209 図5-12 |

|

未 | 未 | 1刷 | 2010.02.02 | ||||||

| 211 図5-14 リファレンス名 |

|

未 | 未 | 1刷 | 2013.08.29 | ||||||

| 211 図5-14 リファレンス名 |

|

未 | 未 | 1刷 | 2013.08.29 | ||||||

| 213 図5-17 R7の定数(ダイオードの下の抵抗値) |

|

未 | 未 | 1刷 | 2013.06.25 | ||||||

| 213 「チェック」14行目 |

|

未 | 未 | 1刷 | 2013.08.29 | ||||||

| 215 図5-20 回路図左上のリファレンスおよび定数 |

|

未 | 未 | 1刷 | 2013.06.25 | ||||||

| 218 図5-23のリファレンスおよび定数 |

|

未 | 未 | 1刷 | 2013.06.25 | ||||||

| 218 5行目 |

|

未 | 未 | 1刷 | 2013.08.29 | ||||||

| 219 図5-25 C3の定数 |

|

未 | 未 | 1刷 | 2013.06.25 | ||||||

| 219 1行目 |

|

未 | 未 | 1刷 | 2013.08.29 | ||||||

| 219 下から5行目 |

|

未 | 未 | 1刷 | 2013.08.29 | ||||||

| 220 図Ex5-1 一番右側の抵抗のリファレンス |

|

未 | 未 | 1刷 | 2013.06.25 | ||||||

| 221 図Ex5-2 中央上 |

|

未 | 未 | 1刷 | 2013.06.25 | ||||||

| 221 「第5章のテスト」4)の(C) |

|

未 | 未 | 1刷 | 2013.08.29 | ||||||

| 222 図Ex5-4 中央と右下(2か所) |

|

未 | 未 | 1刷 | 2013.06.25 | ||||||

| 225 「(4)バンドエリミネートフィルタ(BEF)」の10行目 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 231 「理解度チェック」1)の(B) |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 232 「(4)1次あたり~」の次の行 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 237 式6-6の3行上 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 237 式6-6の2行上 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 239 式6-7の直後の行 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 239 図6-18のキャプション |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 239 下から5行目 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 240 理解度チェック 図Ex6-1 |

|

未 | 未 | 1刷 | 2010.02.02 | ||||||

| 241 ページ右上図のキャプション |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 242 式6-11 4~8行目 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 243 図6-24 抵抗の値 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 243 表6-1 右下隅 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 244 3行目 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 244 式6-12の10行目 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 244 式6-12の7行目 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 245 図Ex6-2 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 246 図6-29 |

|

未 | 未 | 1刷 | 2013.07.16 | ||||||

| 246 図6-28 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 246-247 式6-13の2行目以降 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 247 本文 5行目後半 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 248 図6-30 図中のリファレンス名、定数 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 248 コラム「チェック」 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 248 式の5行目 L5の単位 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 249 図Ex6-3 |

|

未 | 未 | 1刷 | 2013.06.27 | ||||||

| 249 1~3行目 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 249 コラム 2行目 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 250 下から9~7行目 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 252 図6-32 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 252 図6-33 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 252 式6-16 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 255 チェビシェフ多項式のC5とC6の式 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 255 三角関数の加法定理のC2の式の4行目 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 256 チェビシェフ多項式のC5の式 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 256 式6-18 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 260 図6-36 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 260 式6-20 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 264 式6-23 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 264 「(4)状態変数型」の5行上 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 267 式:図6-44(a)利得Gの式の分母右端 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 268 (d)1~2行目(2か所) |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 268 下から4~2行目の式の左辺 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 271 1行目左辺 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 271 図6-46のキャプションの左のテキスト |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 272 式6-26 2本目のC1の式の左辺 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 272 式6-26 5行目 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 273 式6-27「リップル許容度~」の次の行 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 276 式6-28中のCfの式 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 277 図6-53のキャプチャ |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 278 図6-54 「C4」の上 |

|

未 | 未 | 1刷 | 2013.06.25 | ||||||

| 278 式6-29中のCfの式 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 281 式6-30中のCfの式 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 284 下から7行目 Cf2の式の分母 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 285 下から9行目 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 285 下から7行目 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 287 図Ex6-5 |

|

未 | 未 | 1刷 | 2013.06.25 | ||||||

| 298 図7-2(a) |

|

未 | 未 | 1刷 | 2013.06.25 | ||||||

| 309 図7-15 |

|

未 | 未 | 1刷 | 2010.02.02 | ||||||

| 311 下から6行目 |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 320 式8-2の1行上 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 320 式8-3の2行上 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 320 *注(脚注) |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 321 式番号 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 323 式番号 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 323 「変形コルピッツ発振回路」の1行上 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 325 5行目と6行目 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 326 図8-10 定数(4か所) |

|

未 | 未 | 1刷 | 2013.06.25 | ||||||

| 327 下から3~2行目 |

|

未 | 未 | 1刷 | 2013.06.25 | ||||||

| 327 下から12行目 |

|

未 | 未 | 1刷 | 2014.04.07 | ||||||

| 327 2行目と3行目 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 327 式8-7の1行上 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 327 9~10行目 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 327 下から10~9行目 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 328 1行目 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 328 「コルピッツ共振回路の設計」の2行目 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 328 「コルピッツ共振回路の設計」の5行目 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 328 式8-9 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 329 下から3行目 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 332 式8-12の5行上 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 335 下から8行目 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 338 図8-19 |

|

未 | 未 | 1刷 | 2013.06.25 | ||||||

| 338 「コイルレスのコルピッツ型水晶発振回路」の第2段落の1行目 |

|

未 | 未 | 1刷 | 2013.08.30 | ||||||

| 341 図8-20 R1の定数 |

|

未 | 未 | 1刷 | 2013.06.25 | ||||||

| 360 ページ半ば |

|

未 | 未 | 1刷 | 2013.09.02 | ||||||

| 360-361 最下行、1行目 |

|

未 | 未 | 1刷 | 2013.09.02 | ||||||

| 363 下から6~4行目 |

|

未 | 未 | 1刷 | 2013.09.02 | ||||||

| 367 表の1列目 |

|

未 | 未 | 1刷 | 2013.09.02 | ||||||

| 369 「理解度チェック」の3~1行上 |

|

未 | 未 | 1刷 | 2013.09.02 | ||||||

| 373 「デジタル回路のパスコン」の1行上 |

|

未 | 未 | 1刷 | 2013.09.02 | ||||||

| 382 式の下 |

|

未 | 未 | 1刷 | 2013.09.02 | ||||||

| 394 下から10行目 |

|

未 | 未 | 1刷 | 2013.09.02 | ||||||

| 403 図11-5 同期型RSフリップフロップの図 |

|

未 | 未 | 1刷 | 2013.06.25 | ||||||

| 404 「チェック」7行目 |

|

未 | 未 | 1刷 | 2013.09.02 | ||||||

| 404 式11-2の3行上 |

|

未 | 未 | 1刷 | 2013.09.02 | ||||||

| 406 図11-11 真理値表 下から2行目と1行目のTの値 |

|

未 | 未 | 1刷 | 2013.06.25 | ||||||

| 407 図11-16 Tフリップフロップの図 |

|

未 | 未 | 1刷 | 2013.06.25 | ||||||

| 407 式11-3 |

|

未 | 未 | 1刷 | 2013.09.02 | ||||||

| 411 「ホールドタイム」の4~7行目 |

|

未 | 未 | 1刷 | 2013.09.02 | ||||||

| 427 表12-1 「出力」の「次の状態Qn」の2行目 |

|

未 | 未 | 1刷 | 2013.09.02 | ||||||

| 428 表12-3 3行目 |

|

未 | 未 | 1刷 | 2013.09.02 | ||||||

| 430 「理解度チェック」3)最下行 |

|

未 | 未 | 1刷 | 2013.09.02 | ||||||

| 433 下から8~7行目 |

|

未 | 未 | 1刷 | 2013.09.02 | ||||||

| 434 図12-15 LED1の出力 |

|

未 | 未 | 1刷 | 2013.09.02 | ||||||

| 437 図12-18 次のコードのD2/D3の値 |

|

未 | 未 | 1刷 | 2013.09.02 | ||||||

| 437 図12-18 論理式 |

|

未 | 未 | 1刷 | 2013.09.02 | ||||||

| 443 図Ex12-3 |

|

未 | 未 | 1刷 | 2013.09.02 | ||||||

| 443 図Ex12-4 |

|

未 | 未 | 1刷 | 2013.09.02 | ||||||

| 443 9) |

|

未 | 未 | 1刷 | 2013.09.02 | ||||||

| 457 「大文字と小文字」の5行目 |

|

未 | 未 | 1刷 | 2013.09.02 | ||||||

| 459 7行目 |

|

未 | 未 | 1刷 | 2013.09.02 | ||||||

| 463 「演算子」の1~2行目 |

|

未 | 未 | 1刷 | 2013.09.02 | ||||||

| 472 「while~loop文」の1~2行目 |

|

未 | 未 | 1刷 | 2013.09.02 | ||||||

| 476 表13-2「信号に付加されたアトリビュート」の1行上 |

|

未 | 未 | 1刷 | 2013.09.02 | ||||||

| 478 図13-5の下 |

|

未 | 未 | 1刷 | 2013.09.02 | ||||||

| 482 図13-5のキャプション |

|

未 | 未 | 1刷 | 2013.09.02 | ||||||

| 492 11行目 |

|

未 | 未 | 1刷 | 2013.09.02 | ||||||

| 500 (脚注を除き)下から3行目 |

|

未 | 未 | 1刷 | 2013.09.02 | ||||||

| 511 第1章の解答 「ダイオードの概要」(5)、「電界効果トランジスタ(FET)の概要」 2行目 |

|

未 | 未 | 1刷 | 2013.03.13 | ||||||

| 511 第1章のテスト(5) |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 511 第1章のテスト(7) |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 511 第2章「保護回路」(1) |

|

未 | 未 | 1刷 | 2013.06.20 | ||||||

| 513 最下行 |

|

未 | 未 | 1刷 | 2013.06.20 |

ふらく さん

2018-01-19

書いている内容の前に書き方や誤植の多さが問題すぎるクソ本。返品を求めたい。ちなみに誤植は1000か所弱あり、正しい文を推察しても分からない箇所が多々有った。

_sei.jpg)