ディジタル回路設計とコンピュータアーキテクチャ

鈴木 貢 翻訳

鈴木 貢 原著

中條 拓伯 翻訳

中條 拓伯 原著

天野 英晴 翻訳

天野 英晴 原著

David Money Harris 著

Sarah L. Harris 著

永松 礼夫 翻訳

永松 礼夫 原著

- 形式:

- 書籍

- 発売日:

- 2009年08月03日

- ISBN:

- 9784798115344

- 定価:

- 5,280円(本体4,800円+税10%)

- 仕様:

- B5変・656ページ

ヘネ・パタ『コンピュータの構成と設計』を超えた教科書!!

エンジニアやコンピュータ科学者と一般人の違いは、複雑さを管理するのにシステム的(組織的)なアプローチをするかである。最近のディジタルシステムは何十万あるいは何十億個のトランジスタから構成されている、各トランジスタの電子の動きを記述する方程式を書き、その方程式のすべてを同時に満たす解を求めることで、そのようなシステムを理解できるような人間はいない。細かいことの泥沼に嵌らずにマイクロプロセッサを作る方法を理解するには、複雑さを管理する(手懐ける)方法を学ぶべきである。(本文より)

【原題】Digital Design and Computer Architecture

第1章 ゼロからイチへ

1.1 ゲームの計画

1.2 複雑さを管理する方法

1.3 ディジタルによる抽象化

1.4 数の体系

1.5 論理ゲート

1.6 ディジタル抽象化の裏側

1.7 CMOS トランジスタ

1.8 電力消費

1.9 まとめとこれから学ぶこと

第2章 組み合わせ論理回路設計

2.1 はじめに

2.2 ブール論理式

2.3 ブール代数

2.4 論理からゲートへ

2.5 マルチレベル組み合わせ論理回路

2.6 XとZ・・・はて?

2.7 カルノーマップ

2.8 組み合わせ回路のビルディングブロック

2.9 タイミング

2.10 まとめ

第3章 順序回路設計

3.1 はじめに

3.2 ラッチとフリップフロップ

3.3 同期式回路設計

3.4 有限状態マシン

3.5 順序回路のタイミング

3.6 並列性

3.7 まとめ

第4章 ハードウェア記述言語

4.1 はじめに

4.2 組み合わせ回路

4.3 構造モデル化

4.4 順序回路

4.5 組み合わせ回路再考

4.6 有限状態マシン

4.7 パラメータ化モジュール

4.8 テストベンチ

4.9 まとめ

第5章 ディジタルビルディングブロック

5.1 はじめに

5.2 算術演算回路

5.3 数の表現法

5.4 順序回路のビルディングブロック

5.5 メモリアレイ

5.6 ロジックアレイ

5.7 まとめ

第6章 アーキテクチャ

6.1 はじめに

6.2 アセンブリ言語

6.3 機械語

6.4 プログラミング

6.5 番地指定モード

6.6 ライト、カメラ、演技:翻訳、アセンブル、ロード

6.7 諸々

6.8 現実世界の様子:IA-32アーキテクチャ

6.9 まとめ

第7章 マイクロアーキテクチャ

7.1 はじめに

7.2 性能解析

7.3 単一サイクルプロセッサ

7.4 マルチサイクルプロセッサ

7.5 パイプラインプロセッサ

7.6 HDL表現

7.7 例外

7.8 先進的アーキテクチャ

7.9 現実世界の展望:IA-32アーキテクチャ

7.10 まとめ

第8章 メモリシステム

8.1 はじめに

8.2 メモリシステムの性能解析

8.3 キャッシュ

8.4 仮想メモリ

8.5 メモリマップトI/O

8.6 実例:IA-32のメモリとI/Oシステム

8.7 まとめ

例題A ディジタルシステムの実装法

A.1 はじめに

A.2 74xxシリーズ

A.3 プログラマブルロジック

A.4 ASIC

A.5 データシート

A.6 論理回路ファミリ

A.7 パッケージと組み立て

A.8 伝送線路

A.9 経済面

付録B MIPS命令

お問い合わせ

内容についてのお問い合わせは、正誤表、追加情報をご確認後に、お送りいただくようお願いいたします。

正誤表、追加情報に掲載されていない書籍内容へのお問い合わせや

その他書籍に関するお問い合わせは、書籍のお問い合わせフォームからお送りください。

利用許諾に関するお問い合わせ

本書の書影(表紙画像)をご利用になりたい場合は書影許諾申請フォームから申請をお願いいたします。

書影(表紙画像)以外のご利用については、こちらからお問い合わせください。

-

viiページの「オンライン補助教材」提供サイトについて

本書刊行後に「オンライン補助教材」提供サイトのURLが変更になったようです。

現在はこちらからダウンロードができます。

http://booksite.elsevier.com/9780123704979/

※2014年7月31日現在の情報です。

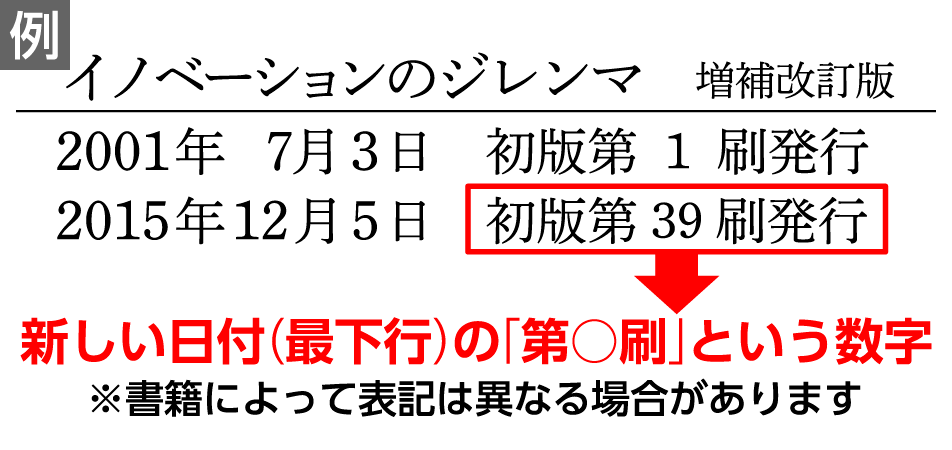

ご購入いただいた書籍の種類を選択してください。

書籍の刷数を選択してください。

刷数は奥付(書籍の最終ページ)に記載されています。

現在表示されている正誤表の対象書籍

書籍の種類:

書籍の刷数:

本書に誤りまたは不十分な記述がありました。下記のとおり訂正し、お詫び申し上げます。

対象の書籍は正誤表がありません。

| 発生刷 | ページ数 | 書籍改訂刷 | 電子書籍訂正 | 内容 | 登録日 | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| 1刷 | 059 図2.13 見出し行 |

2刷 | 未 |

|

2011.04.15 | ||||||

| 1刷 | 129 図3.22 キャプション |

2刷 | 未 |

|

2010.10.28 | ||||||

| 1刷 | 133 表3.4のキャプション |

2刷 | 未 |

|

2013.06.10 | ||||||

| 1刷 | 153 例題3.9 5行目 |

3刷 | 未 |

|

2014.08.22 | ||||||

| 1刷 | 263 5行目 |

2刷 | 未 |

|

2013.05.27 | ||||||

| 1刷 | 264 例題5.2の解法 1行目 |

2刷 | 未 |

|

2013.05.27 | ||||||

| 1刷 | 269 5行目 |

2刷 | 未 |

|

2013.05.27 | ||||||

| 1刷 | 269 例題5.3 1行目 |

2刷 | 未 |

|

2013.05.27 | ||||||

| 1刷 | 271 図5.17 |

2刷 | 未 |

|

2009.07.29 | ||||||

| 1刷 | 273 除算のコードの訂正とアルゴリズムについての訳注追加 |

3刷 | 未 |

|

2014.12.26 | ||||||

| 1刷 | 295 本文下から3行目 |

2刷 | 未 |

|

2013.05.27 | ||||||

| 1刷 | 346 コード例6.22 右側「MIPSアセンブリコード」上から9行目 |

2刷 | 未 |

|

2013.06.10 | ||||||

| 1刷 | 408 表7.2の3行目のALUOp欄 |

2刷 | 未 |

|

2013.06.10 | ||||||

| 1刷 | 413 式7.2 |

2刷 | 未 |

|

2013.05.27 | ||||||

| 1刷 | 418 6行目、11行目(2か所) |

2刷 | 未 |

|

2013.05.27 | ||||||

| 1刷 | 434 5行目 |

2刷 | 未 |

|

2013.06.10 | ||||||

| 1刷 | 434 例題7.8の解法の5行目 |

2刷 | 未 |

|

2013.06.10 | ||||||

| 1刷 | 455 下から10行目 |

2刷 | 未 |

|

2013.05.27 | ||||||

| 1刷 | 498 演習7.17 3行目 |

2刷 | 未 |

|

2013.05.27 | ||||||

| 1刷 | 613 右側の列 中央より下 |

2刷 | 未 |

|

2009.09.30 |

MATSUDA, Shougo さん

論理回路設計名著の和訳版。とりあえずFPGA/ASICの論理回路設計を習得したければ一読必須。基本〜中級までで幅広く抑えているのでこれを理解した上で各個技術の掘り下げに着手するのが最良かと。

Tomotaka Hosotani さん

コンピュータ設計の入門として読んでみたけど、、、なかなか分かりやすい。CPUと周辺回路など幅広く解説されているのが良かった。

.png)